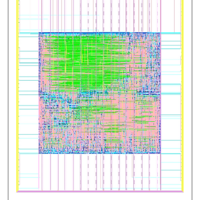

Coriolis RTL-to-GDSII Toolchain

State of advancement and planned improvements

- Track: Libre-Open VLSI and FPGA devroom

- Room: D.open-hardware

- Day: Sunday

- Start: 10:30

- End: 11:20

- Video with Q&A: D.open_hardware

- Video only: D.open_hardware

- Chat: Join the conversation!

Sorbonne Université, in collaboration with Chips4Makers and LibreSOC are working to provide a complete FOSS toolchain to make ASICs in mature technological nodes, that is, no smaller than 130nm. We take a circuit description in HDL, synthetize with Yosys but instead of targetting a FPGA, use an ASIC standard cell library to get the RTL description. From there, with Coriolis2, we perform the classical steps of a RTL to GDSII flow, that is, placement, routage along with very basic timing closure.

We will particularly focus on last year progresses and present the planned improvements and new features for 2022.

Speakers

| Jean-Paul Chaput |