# Can we do an open source chip design in 45 minutes?

Philipp Wagner FOSDEM 2023

Terms and conditions apply. Sit through this talk for details.

#### **Our Agenda**

- The technology: tools & processes to build an open source chip.

- The community: how we're working together.

- The future.

#### **About Philipp**

philipp@fossi-foundation.org

@imphil on GitHub

@MrImphil on Twitter

#### **About FOSSi Foundation**

The FOSSi Foundation exists to promote and protect the open source silicon chip movement. It actively encourages the community's growth and is helping to maintain the open spirit of the movement, through events, educational programmes and working groups. With an international membership of experts from academia and industry, it supports new open source initiatives and collaborations – offering free advice to governments and policy makers, corporations, academics and hobbyists. As a not-for profit organisation, the foundation is independent of any commercial interests and acts as a steward in support of open source projects which broadly benefit the open source silicon community. FOSSi is an acronym for Free and Open Source Silicon.

## Technology

#### How to build a chip?

Implement the chip's functionality

Realize this functionality in the physical world

Logic Physics

### Frontend

Program the chip's functionality.

#### **Just like programming**

"Programming languages"

**High-Level Synthesis (HLS)**

**High-Level Languages**

SystemVerilog and VHDL

**Netlist**

"All the other stuff"

**Test Frameworks**

**Build tools**

**Developer productivity**

**Simulators**

#### **Hardware description**

- (System)Verilog

- VHDL

- BlueSpec (Verilog/Haskell)

- Python-based

- Migen

- Amaranth HDL

- MyHDL

- Based on functional programming languages

- Spinal-HDL (Scala)

- Chisel (Scala)

- Clash (Haskell)

- CIRCT: LLVM

#### **Reuse and integrate**

- LiteX

- (OpenCores)

- ...

#### What can we do with a logic design?

- Verify it

- Document it

- Make it look pretty

- Simulate it

- Run it on an FPGA

#### **Simulate it**

**NVC**

#### **Verification frameworks**

#### **SymbiYosys**

#### **Build and run**

- FuseSoC and Edalize

- VUnit

- bazel\_rules\_hdl

- HDLMake

- •

#### **Developer productivity**

- Verible: lint, formatter, code indexer, language server, and more

- Formatting based mostly on the <u>lowRISC SV Style Guide</u>

- Verilator lint

- VHDL Style Guide (VSG)

- •

#### **Verilator lint**

%Warning-WIDTH: ../src/lowrisc\_ip\_alert\_handler\_component\_0.1/rtl/alert\_handler\_ping\_timer.sv:131:58: Operator GTE expects 32 bits on the LHS, but LHS's SEL generates 7 bits.

%Warning-WIDTH: ../src/lowrisc\_ip\_alert\_handler\_component\_0.1/rtl/alert\_handler\_ping\_timer.sv:132:57: Operator SUB expects 32 bits on the LHS, but LHS's SEL generates 7 bits.

%Warning-WIDTH: ../src/lowrisc\_ip\_alert\_handler\_component\_0.1/rtl/alert\_handler\_ping\_timer.sv:131:70: Operator COND expects 32 bits on the Conditional False, but Conditional False's SEL generates 7 bits.

%Warning-WIDTH: ../src/lowrisc\_ip\_alert\_handler\_component\_0.1/rtl/alert\_handler\_ping\_timer.sv:131:23: Operator ASSIGNW expects 7 bits on the Assign RHS, but Assign RHS's COND generates 32 bits.

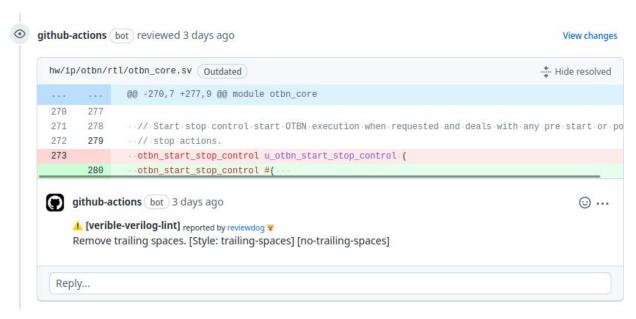

#### **Automate reviews with Verible lint**

Screenshot from https://github.com/lowRISC/opentitan/pull/17195

#### **Automate reviews with Verible lint**

```

hw/ip/otbn/rtl/otbn_core.sv Outdated

· Hide resolved

@@ -878,7 +889,14 @@

878

889

879

--//-Advance-URND-either-when-the-start_stop_control-commands-it-or-when-temporary-secure-wipe

...// are requested.

881

assign urnd_advance = urnd_advance_start_stop_control | req_sec_wipe_urnd_keys_q;

892

- if (!SecMuteUrnd) begin

github-actions bot 3 days ago

(·) ···

▲ [verible-verilog-lint] reported by reviewdog *

All generate block statements must have a label [Style: generate-statements] [generate-label]

Reply...

```

Screenshot from https://github.com/lowRISC/opentitan/pull/17195

#### **Summary**

- The frontend is doing great.

- If we could only avoid re-inventing Verilog parsing.

## Backend

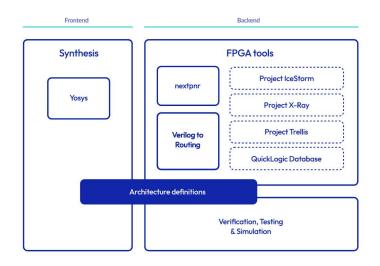

## Run your design on an FPGA

#### Run it on an FPGA

#### F4FPGA (formerly SymbiFlow)

|                 | Project<br>Icestorm | Project<br>Trellis | Project<br>X-Ray | QuickLogic<br>Database |

|-----------------|---------------------|--------------------|------------------|------------------------|

| Basic Tiles:    | <b>~</b>            | ~                  | <b>&gt;</b>      | ~                      |

| - Logic         | ~                   | ~                  | ~                | ~                      |

| - Block RAM     | ~                   | ~                  | <b>*</b>         | ~                      |

| Advanced Tiles: | ~                   | ~                  | <b>×</b>         | ~                      |

| - DSP           | ~                   | ~                  | ×                | ~                      |

| - Hard Blocks   | <b>~</b>            | ~                  | ×                | ~                      |

| - Clock Tiles   | <b>~</b>            | ~                  | ~                | ~                      |

| - IO Tiles      | ~                   | ~                  | ~                | ~                      |

| Routing:        | ~                   | ~                  | ~                | ~                      |

| - Logic         | ~                   | ~                  | ~                | ~                      |

| - Clock         | <b>~</b>            | _                  | ~                | _                      |

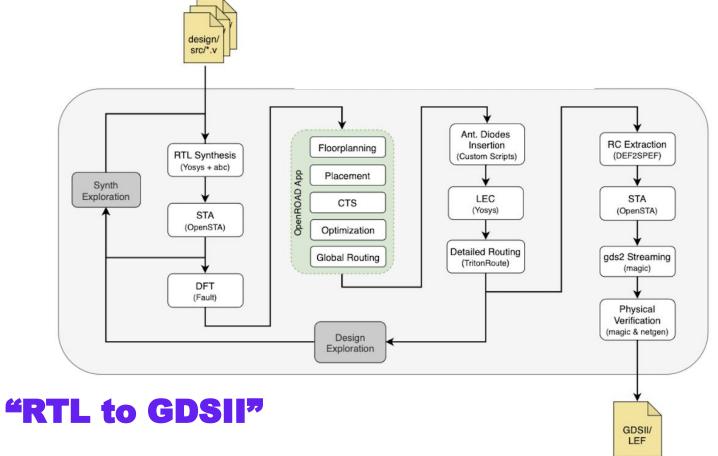

## Backend

## Design the physical implementation

03

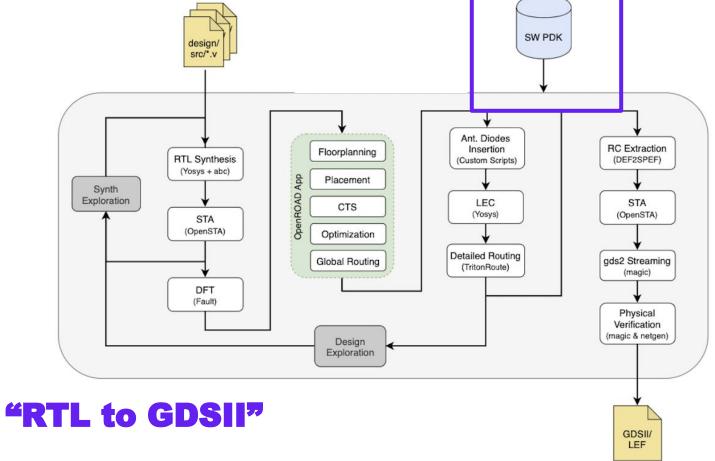

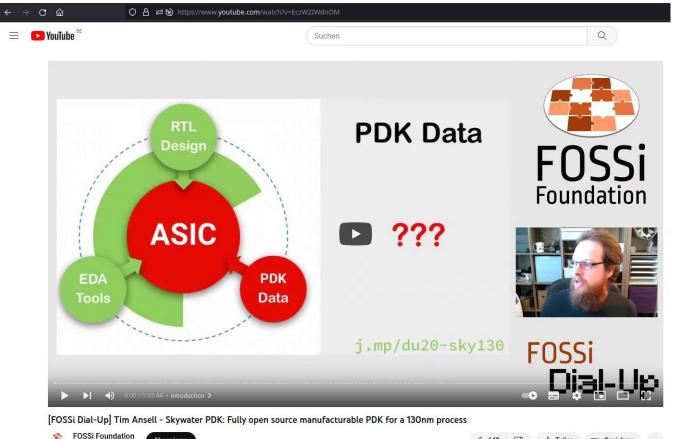

## The Process Design Kit (PDK)

#### The Design Kit

- standard cell libraries, design rules, electrical parameters, ...

- get it from the foundry

- bad: requires pretty tough NDA

- good: it's usually for free (again, as in beer)

FOSDEM 201

Digital Hardware Design - Why is it still so hard?

#### "The ASIC Check": Results

• Hobbyist-Accessibility-Score: 0.1/5

• FOSS score: 1/5

• Fun score: 1-5/5

• Satisfaction score: 10/5

let's do it anyways?

EOSDEM 2016

Digital Hardware Design - Why is it still so hard?

MULTIMEDIA-Tastatur:

Inklusive auswechselbaren

3-Tasten-Wheel-Mouse:

Inklusive Mouse-Pad

Handballen-Auflagen in 3 Farben

Westere

Informationen

erhalten Sie

in unserem

**Handzettell**

ne

ssezilet:

is ...

ur AMD'

wieder

Software-Angebot

#### Make Your Own Chips for Free

Design and fabricate your own open-source design for free with the Open MPW Program

MPW-7 Submission Deadline is September 12

#### Welcome to the Efabless Open MPW Program

The shuttle provides apportunities for designers to

## The future of Intel's manufacturing processes

by Anand Lal Shimpi on December 11, 2000 1:23 AM EST

"Realistically speaking, we should be able to see **NetBurst based processors reach somewhere between 8 – 10GHz in the next five years**before the architecture is replaced yet again. Reaching 2GHz isn't much of a milestone, however reaching 8 – 10GHz begins to make things much more exciting than they are today. Obviously this 8 – 10GHz clock range would be based on Intel's 0.07-micron process that is forecasted to debut in 2005. These processors will run at less than 1 volt, 0.85v being the current estimate."

https://www.anandtech.com/show/680/6

#### Installing EDA tools has never been easier

- \$ git clone https://github.com/The-OpenROAD-Project/OpenLane

- \$ cd OpenLane

- \$ make

- \$ make test

- \$ make mount

Additionally used for demo: <a href="https://github.com/mattvenn/openlane\_summary">https://github.com/mattvenn/openlane\_summary</a>

#### **OpenLane demo**

```

$ flow.tcl -design spm -tag my-spm

$ flow.tcl -design spm -tag my-spm -gui

$ ./openlane_summary/summary.py --design spm --summary

$ ./openlane_summary/summary.py --design spm --yosys-report

$ ./openlane_summary/summary.py --design spm --gds

```

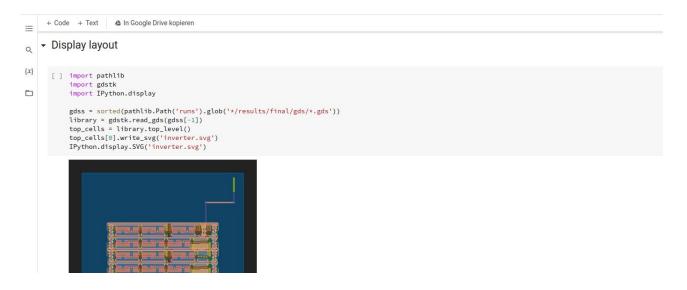

#### **Online chip development**

digital-inverter-openlane.ipynb - Colaboratory

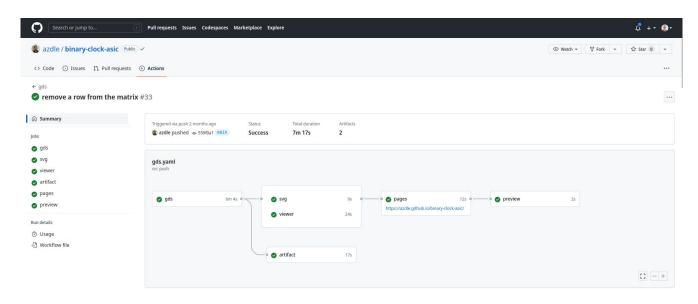

#### **Tiny Tapeout CI**

**GH Actions view; GDS view**

# People

#### Yosys

## 2.5k stars on GitHub A recent month in Yosys:

Excluding merges, **10 authors** have pushed **44 commits** to master and **48 commits** to all branches. On master, **80 files** have changed and there have been **6,027 additions** and **382 deletions**.

#### **Verilator**

1.5k stars on GitHub

A recent month in Verilator:

Excluding merges, **20 authors** have pushed **94 commits** to master and **96 commits** to all branches. On master, **534 files** have changed and there have been **7,073 additions** and **2,375 deletions**.

#### cocotb

### 1.3k stars on GitHub A recent month in cocotb:

Excluding merges, **7 authors** have pushed **11 commits** to master and **12 commits** to all branches. On master, **23 files** have changed and there have been **295** additions and **23 deletions**.

#### **Skwater 130 PDK**

## 2.5k stars on GitHub A recent month in Skywater:

Excluding merges, 1 author has pushed 1 commit to main and 1 commit to all branches. On main, 1 file has changed and there have been 1 additions and 1 deletions.

#### **OpenLane**

800 stars on GitHub

A recent month in OpenLane:

Excluding merges, **7 authors** have pushed **25 commits** to master and **25 commits** to all branches. On master, **58 files** have changed and there have been **1,101 additions** and **1,384 deletions**.

#### **OpenROAD**

725 stars on GitHub

A recent month in OpenROAD:

Excluding merges, **19 authors** have pushed **325 commits** to master and **325 commits** to all branches. On master, **583 files** have changed and there have been **46,241 additions** and **390,554 deletions**.

#### Linux

#### A recent month in the Linux Kernel:

Excluding merges, **505 authors** have pushed **1,021 commits** to master and **1,021 commits** to all branches. On master, **1,430 files** have changed and there have been **18,570 additions** and **9,814 deletions**.

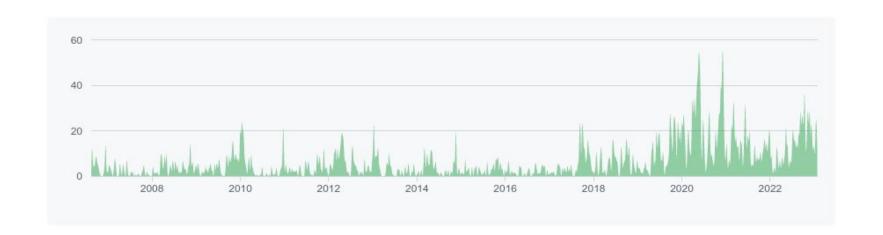

#### Verilator, a growing community

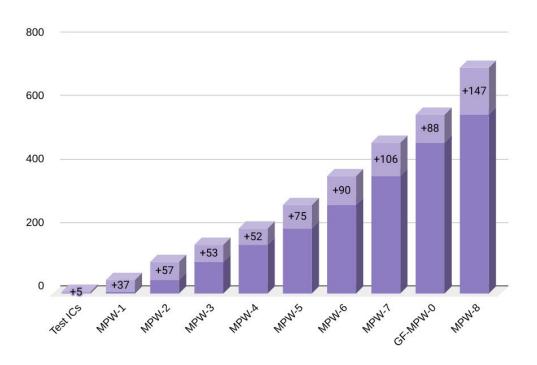

#### More chip designs!

Number of chip designs **submitted** to OpenMPW – not all of them are being manufactured!

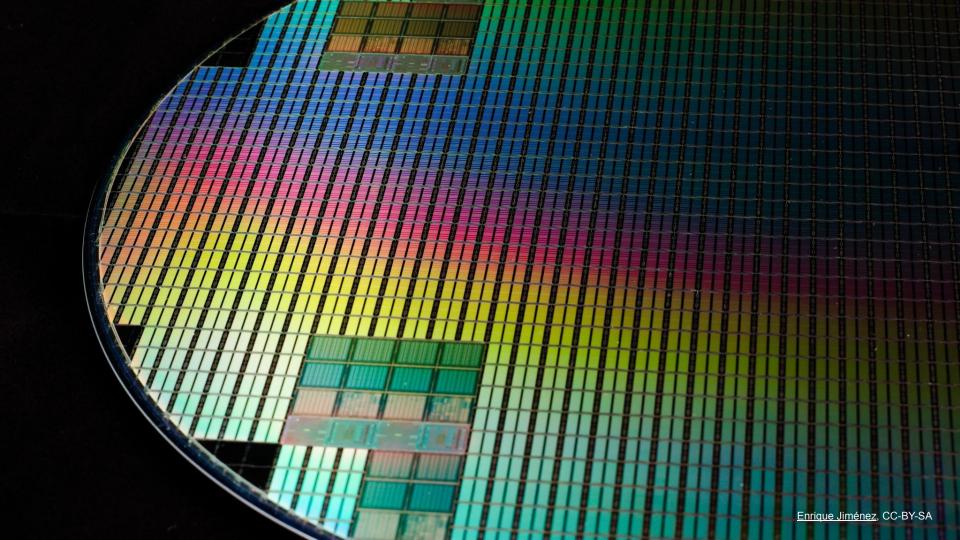

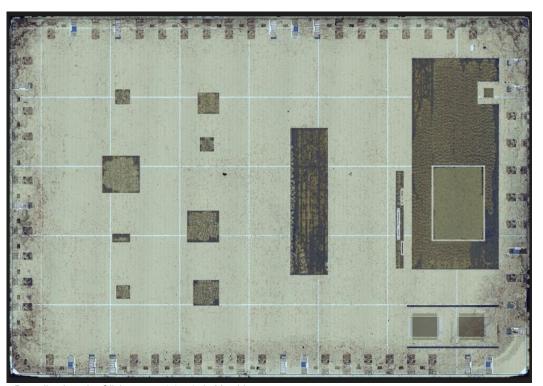

#### **Chips are back!**

Bare die photo by Olivier at texplained via Matt Venn.

## The Future

#### What does the future hold?

- Unpredictable innovation.

- Simpler, more accessible, better tools.

- Democratized access! (part of it: cost)

- Revolutionize learning!

#### **Learn more**

- El Correo Libre, the monthly FOSSi Foundation newsletter.

<a href="https://www.fossi-foundation.org/ecl">https://www.fossi-foundation.org/ecl</a>

- Join the open-source-silicon.dev Slack with all your questions

- Give it a try: Submit to OpenMPW!

- Learn, literally! Take the Zero to ASIC Course or do a Tiny Tapeout (thanks Matt!)

#### **In-person events are back!**

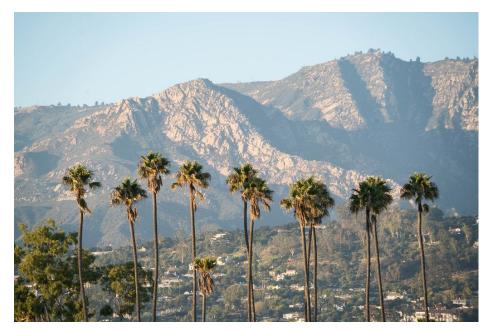

ChrisGoldNY CC BY 3.0

#### Latch-Up 2023

Friday, March 31 to Sunday, April 2, 2023 Santa Barbara, CA, USA

https://latchup.io

#### **In-person events are back!**

Hochschule München, CC BY-SA 4.0, via Wikimedia Commons

#### **ORConf 2023**

September 15 - 16, 2023 Munich, Germany

https://orconf.org/

An atmosphere of excitement and anticipation pervades this field. Workers from many backgrounds, computer scientists, electrical engineers, and physicists, are collaborating on a common problem area which has not yet become classical. The territory is vast, and largely unexplored. The rewards are great for those who simply press forward.

C. Mead and L. Conway, Introduction to VLSI systems. Addison-Wesley Reading, MA, 1978.

Free and Open Source Silicon is a reality today.

Join the fun!