# **Advanced PCB simulation with KiCad**

Introduction to IBIS and FEM-based simulations

**Fabien CORONA**

**FOSDEM 2022**

05/02/2022

# SUMMARY

- Present state of simulation in KiCad

- FEM simulations

- Power integrity

- Signal integrity

- IBIS

# Present state of simulation in KiCad

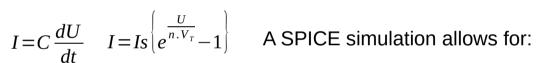

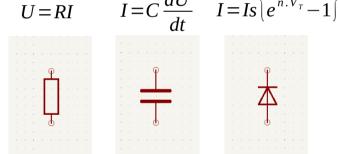

SPICE = "Simulation Program with Integrated Circuit Emphasis"

KiCad provides a graphical interface to a spice engine: ngspice.

A simulation provides a way to design and to validate a project.

- Time response analysis

- Frequency response analysis

- DC analysis

- Much more...

But we cannot model everything...

# **FEM: Finite Element Method**

#### What is FEM?

#### Maxwell's equations

$\nabla \cdot E = \frac{\rho}{\epsilon_0}$

$\nabla \cdot B = 0$

$\nabla \times E = \frac{-\partial B}{\partial t}$  $\nabla \times B = \mu_0 (J + \epsilon_0 \frac{\partial E}{\partial t})$

Electric charges contribute to the electric field

There is no magnetic monopole

A changing magnetic field creates an electric force

Electric currents create magnetic fields,

a changing electric field behaves like a current

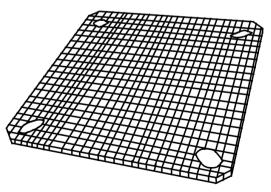

FEM: Slice the board into small domains, then solve Maxwell's equations on each domain

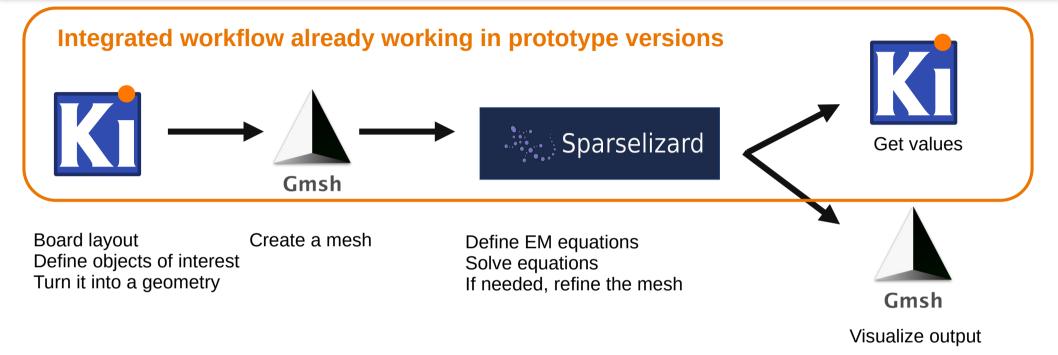

#### **FEM: workflow**

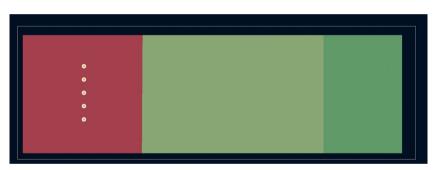

# **Power integrity**

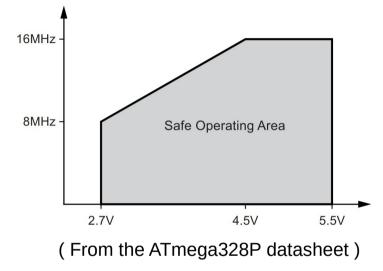

In the gray area, the device should work as expected Outside, it may or may not work We may face:

- A power off

- Resets

- Glitches

- $\rightarrow$  We have to stay in the safe operating area

A good power integrity also helps with EMI (Electromagnetic interference)

#### **Electrical Characteristics** (@T<sub>A</sub> = +25°C, unless otherwise specified.)

| Characteristic                  | Symbol   | Min  | Тур  | Max  | Unit  | Test Condition                                        |

|---------------------------------|----------|------|------|------|-------|-------------------------------------------------------|

| Output Voltage (Note 12)        | Vout     | 4.75 | 5.0  | 5.25 | V     | $V_{IN} = 12V, I_{OUT} = 15mA$                        |

|                                 |          | _    | 33   | 220  |       | $V_{IN} = 10V$ to 15V, $I_{OUT} = 15mA$               |

| Line Regulation (Notes 12 & 13) | ΔVουτ    | _    | 400  | 700  | mV    | $V_{IN} = 7V$ to 60V, $I_{OUT} = 15$ mA               |

|                                 |          | _    | 145  | 400  |       | V <sub>IN</sub> = 10V to 60V, I <sub>OUT</sub> = 15mA |

| Temperature Coefficient         | ΔVουτ/ΔΤ |      | 3.52 |      | mV/°C | T <sub>J</sub> = -40°C to +150°C                      |

|                                 |          |      | 0.02 |      |       | $V_{IN} = 12V, I_{OUT} = 15mA$                        |

| Load Regulation (Notes 12 & 14) | ΔVουτ    | _    | -20  | -130 | mV    | $I_{OUT} = 10$ mA to 20mA, $V_{IN} = 12V$             |

|                                 |          |      | -166 | -300 |       | $I_{OUT} = 0.1$ mA to 50mA, $V_{IN} = 12V$            |

#### Voltage regulators are not perfect:

- DC voltage can be different from the nominal voltage

- The load regulation is not perfect

5V R L 4.85V SUPPLY DEVICE

The power delivery network ( PDN ) is not perfect:

- The copper resistivity leads to a DC voltage drop

- Its inductance leads to a frequency-dependent voltage drop

## **Power integrity: Mitigation**

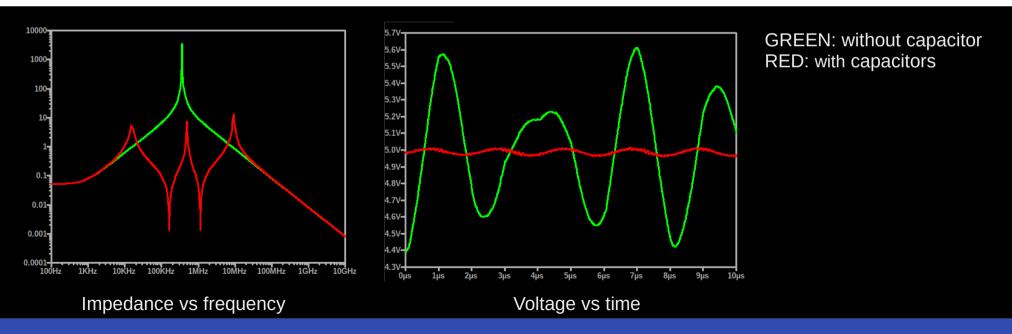

#### The voltage drop is $U(f) = Z(f) \cdot I(f)$

We want the voltage drop to be lower than a target voltage, Uo. U(f) < Uo(f)Which is equivalent the impedance being lower than a target impedance, Zo. Z(f) < Zo(f)The target impedance

# The target impedance depends on the application

We add capacitors to lower the impedance. At high frequencies, we rely on the capacitance provided by the PCB itself

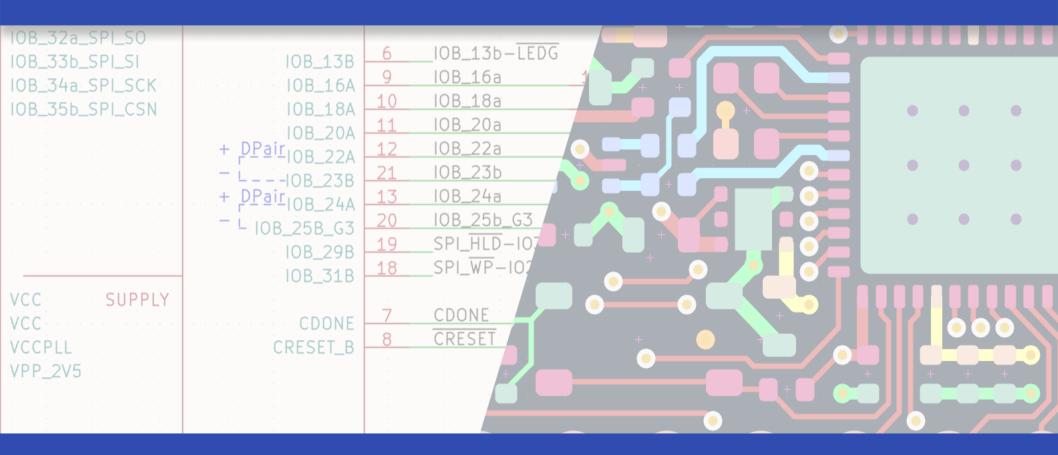

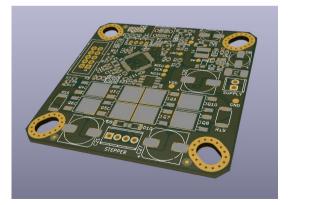

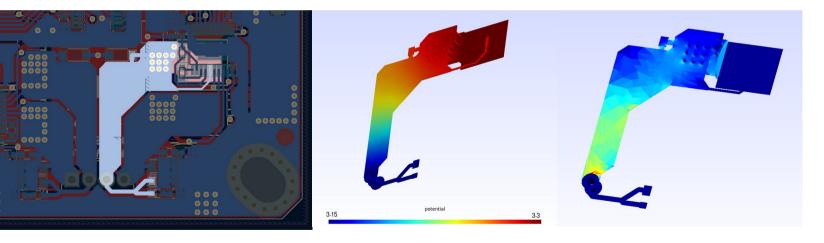

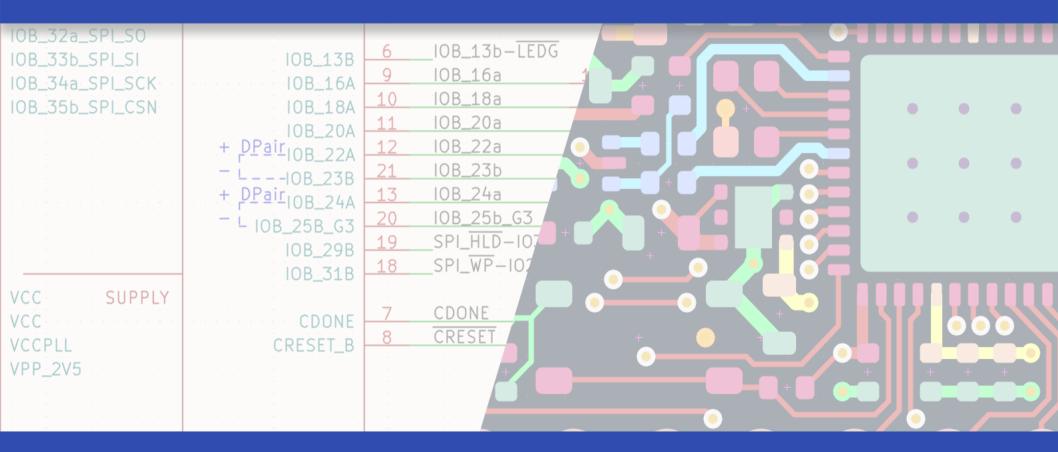

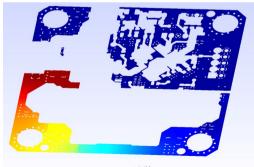

### FEM: Application example – Voltage drop (3D)

Related applications:

- Visualization of potential / current distribution

- Via stress analysis

- Resistance of complex geometries (copper zones)

- AC variant  $\rightarrow$  Power delivery network impedance

PCB editor

Electric potential

Current density

## **FEM:** Application example – Voltage drop - Setup

The user chooses a net. The user defines voltage sources and current sinks. There can be multiple sources, and multiple sinks.

| Simulations                            | Electrical                                |           |     |         |       |      |

|----------------------------------------|-------------------------------------------|-----------|-----|---------|-------|------|

| DC Power Analysis<br>Plane Capacitance | Select a net +3V3                         |           |     |         |       |      |

|                                        | NOTE : Unit is V for sources, A for sinks |           |     |         |       |      |

|                                        |                                           | Component | Pad | Туре    | Value | Unit |

|                                        | 6                                         | L1        | 1   | passive |       | -    |

|                                        | 7                                         | P1        | 1   | passive |       | -    |

|                                        | 8                                         | R3        | 2   | passive |       | -    |

|                                        | 9                                         | U4        | 17  | source  | 3.3   | v    |

|                                        | 10                                        | U4        | 36  | sink    | 1.5   | A    |

|                                        | 11                                        | U4        | 44  | sink    | 0.3   | A    |

|                                        | 12                                        | U2        | 5   | sink    | 0.15  | A    |

|                                        | 13                                        | ₩5        | 1   | passive |       |      |

|                                        | 14                                        | R23       | 2   | passive |       | -    |

|                                        | 15                                        | R24       | 2   | passive |       | -    |

|                                        | 16                                        | U9        | 8   | passive |       | -    |

|                                        | 17                                        | C37       | 2   | passive |       | ->   |

|                                        | 1                                         |           |     | I .     |       | 1 1  |

(This GUI is for development purposes)

| Outputs    |                |               |           |     |

|------------|----------------|---------------|-----------|-----|

| 🛃 Gener    | ate 3D map : j | potential dro | р         |     |

| Conor      | ate 3D map : o | urrent dens   | ity       |     |

|            |                |               |           |     |

| Gener      | ate 3D map : j | power densit  | y density |     |

| 🗹 Gener    |                |               |           |     |

| IOTE: you  | ı can use gmsh | n to open 3D  | maps      |     |

| elect a fo | lder for outpu | its: (N       |           | •   |

|            | A              | В             | c         | D   |

| 8          | <br>R3         | 2             | 3.32287   | v   |

| 9          | U4             | 17            | 1.95      | A   |

| 10         | U4             | 36            | 3.32478   | V   |

| 11         | U4             | 44            | 3.32287   | v   |

| 12         | U2             | 5             | 3.33002   | v   |

| 13         | W5             | 1             | 3.32942   | V   |

| 14         | R23            | 2             | 3.3       | v   |

| 15         | R24            | 2             | 3.32866   | v   |

| 16         | U9             | 8             | 3.3       | v   |

| 17         | C37            | 2             | 3.3       | v   |

| 18         | P4             | 4             | 3.32287   | v   |

| 19         | C4             | 2             | 3.3       | V   |

| 20         | C6             | 2             | 3.32281   | V   |

| 21         | R12            | 1             | 3.32801   | V   |

| 22         | R13            | 1             | 3.32834   | V   |

| 23         | U1             | 11            | 3.3       | V   |

| 24         | U1             | 12            | 3.3       | V   |

| 25         | U3             | 8             | 3.32281   | V T |

## **FEM:** Application example – Capacitance

Related applications:

- Power integrity (plane capacitance)

- Some RF applications?

## **FEM:** Application example – Capacitance - Setup

| <ul> <li>Board Stackup</li> <li>Board Editor Layers</li> </ul> | Copper layers: 4     | •                  | Impedance     | controlled              |           |   | Add Dielectric Layer |         | vielectric Layer  |

|----------------------------------------------------------------|----------------------|--------------------|---------------|-------------------------|-----------|---|----------------------|---------|-------------------|

| Physical Stackup<br>Board Finish                               | Laye Id              | Турғ               | Materia       |                         | Thickne   | Ĥ | Colo                 | Epsilon | Loss              |

| Solder Mask/Paste                                              | F.Silkscreen         | Top Silk Screen    | Not specified |                         |           |   | Not specified 🔻      |         |                   |

| <ul> <li>Text &amp; Graphics</li> </ul>                        | F.Paste              | Top Solder Paste   |               |                         |           |   |                      |         |                   |

| Defaults<br>Fomatting                                          | F.Mask               | Top Solder Mask    | Not specified |                         | 0.01 mm   |   | Not specified 🔻      | 3.3     | 0                 |

| Text Variables                                                 | F.Cu                 | Copper             |               |                         | 0.035 mm  |   |                      |         |                   |

| <ul> <li>Design Rules</li> <li>Constraints</li> </ul>          | Dielectric 1         | Core 👻             | FR4           |                         | 2.51 mm   |   | Not specified 🔻      |         | 0.02              |

| Pre-defined Sizes                                              | In1.Cu               | Copper             |               |                         | 0.035 mm  |   |                      |         |                   |

| Net Classes<br>Custom Rules                                    | Dielectric 2         | PrePreg 👻          | FR4           |                         | 2.51 mm   |   | Not specified 🔻      |         | 0.02              |

| Violation Severity                                             | In2.Cu               | Copper             |               |                         | 0.035 mm  |   |                      |         |                   |

|                                                                | Dielectric 3         | Core 👻             | FR4           |                         | 2.51 mm   |   | Not specified 🔻      |         | 0.02              |

|                                                                | B.Cu                 | Copper             |               |                         | 0.035 mm  |   |                      |         |                   |

|                                                                | Board thickness fror | n stackup: 7.69 mm | Adjust D      | vielectric <sup>-</sup> | Thickness |   |                      | Exp     | oort to Clipboard |

| Import Settings from Anot                                      | her Board            |                    |               |                         |           |   |                      | © Cance | і 🗸 ок            |

#### (This GUI is for development purposes)

| Electrical      |                  |              |   |  |

|-----------------|------------------|--------------|---|--|

| Select a net    | A -              |              |   |  |

| Select a net    | в                |              |   |  |

| Outputs         |                  |              |   |  |

| 🛃 Generate      | 3D map : charg   | ge density   |   |  |

| 🛃 Generate      | 3D map : Elect   | ric field    |   |  |

| NOTE: you can   | use gmsh to c    | open 3D maps |   |  |

| Select a folder | for outputs:     | (None)       | - |  |

| Results         |                  |              |   |  |

| Simulated cap   | acitance is 0.44 | 46199nF      |   |  |

Run

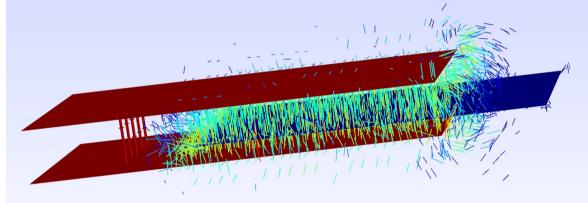

# **Signal integrity**

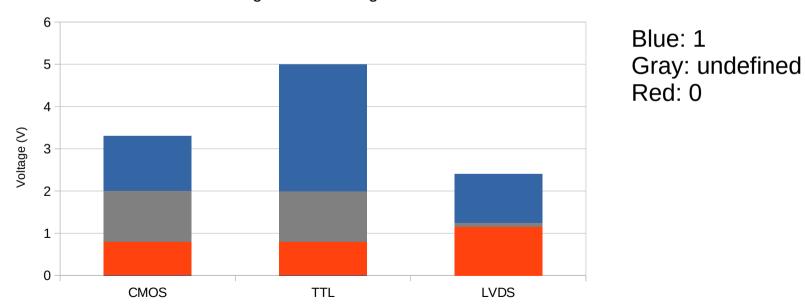

1s and 0s are digital information, and can only take two values. We use analog signals to transmit bits which can take any value. Between 1 and 0, there is always an undefined value.

Threshold voltages for some logic families

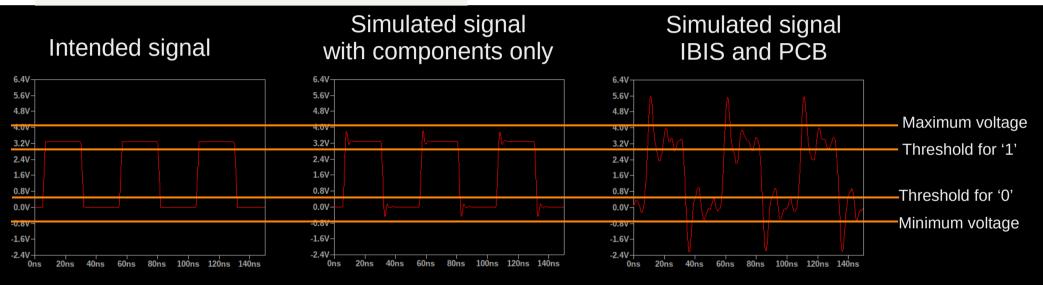

## Signal integrity: what can go wrong

Exceeding the safe voltage range of the component can deteriorate the component. Crossing multiple times can lead to multiple captures.

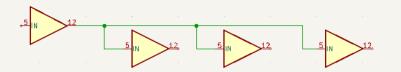

Any track has a characteristic impedance defined by its capacitance and its inductance.

Maintaining a constant impedance is a key for signal integrity.

The receiver should match the track impedance.

This is not a high-frequency problem, but a low rise time problem.

Blue: 0 % matching Yellow: 66 % matching Red: 100 % matching

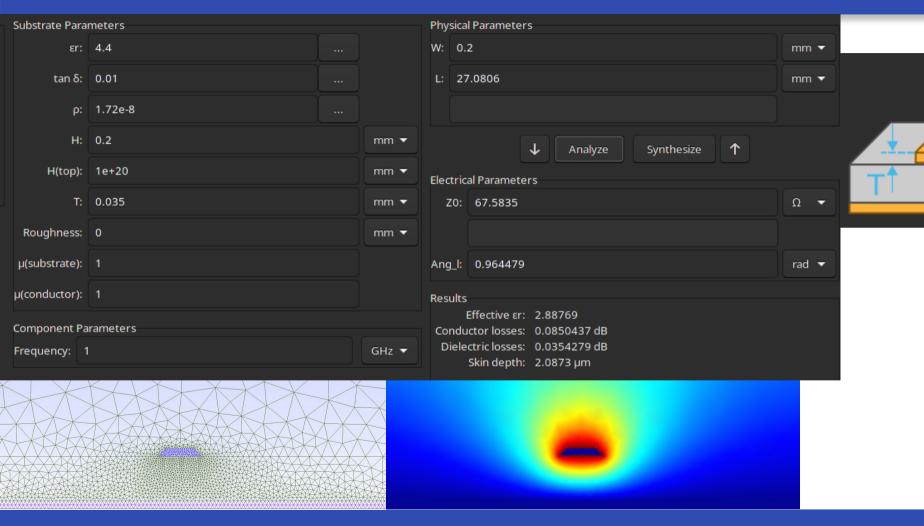

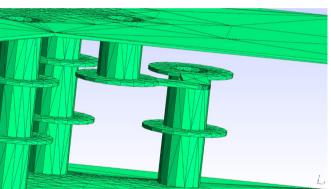

## FEM: Application example – Track impedance - Setup

W

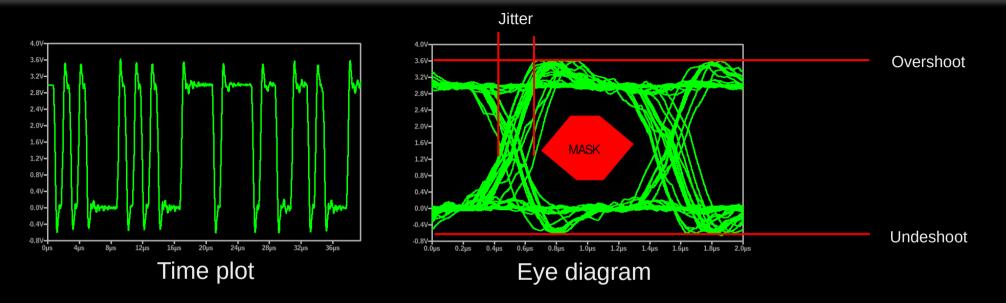

## Signal Integrity: Eye diagram

The eye diagram is a compliance test Using a random sequence, we can measure the ISI (inter symbol interference) The signal should not enter the mask

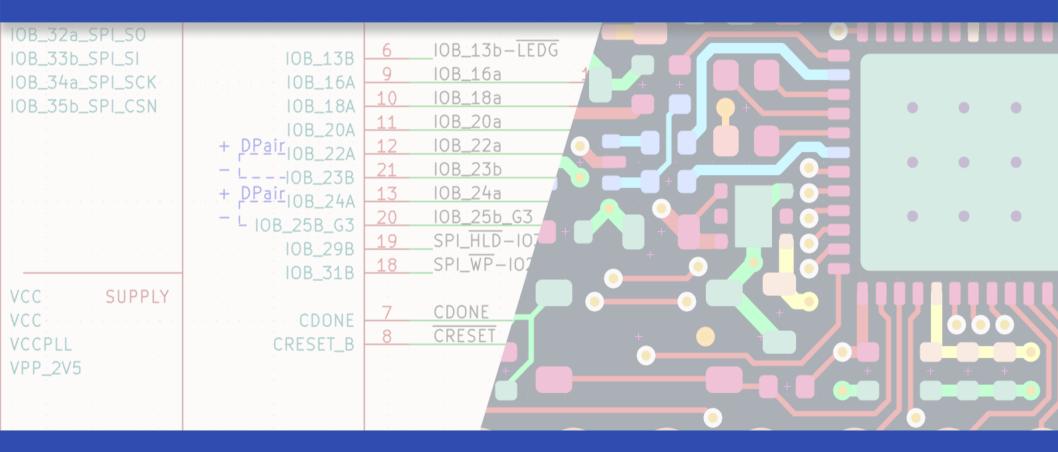

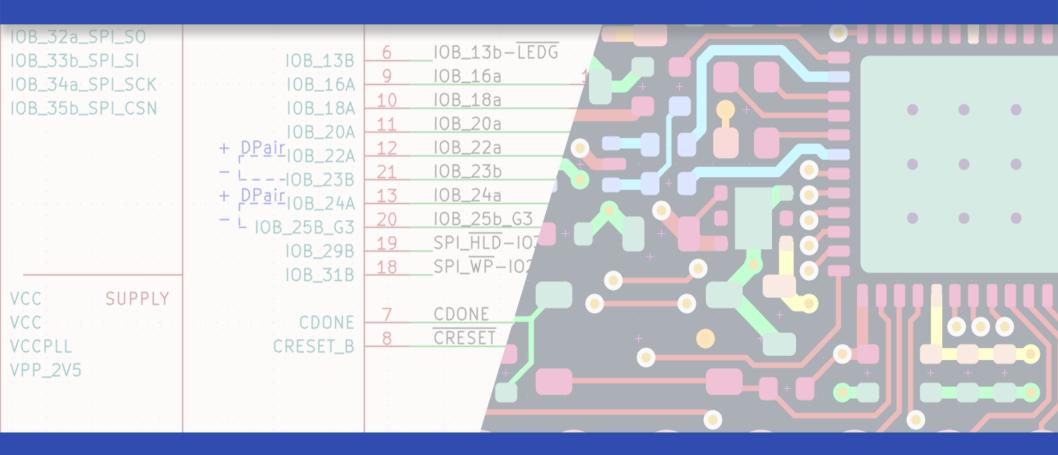

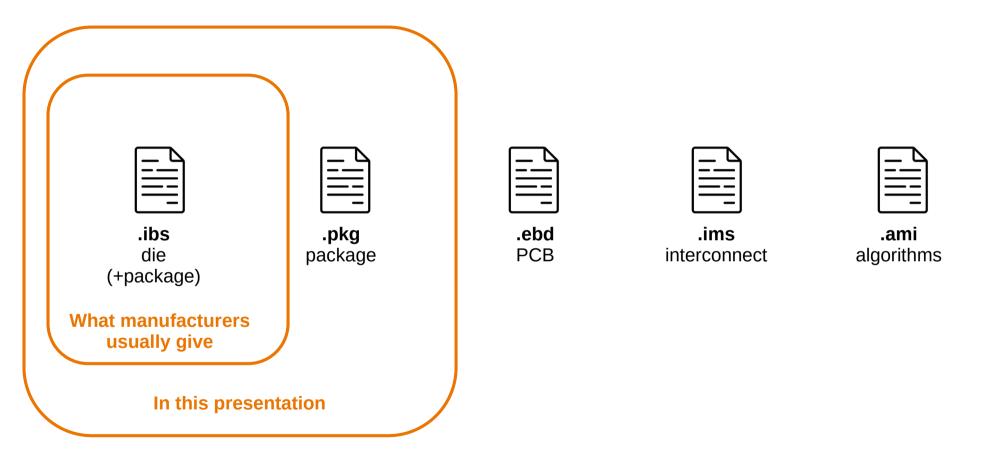

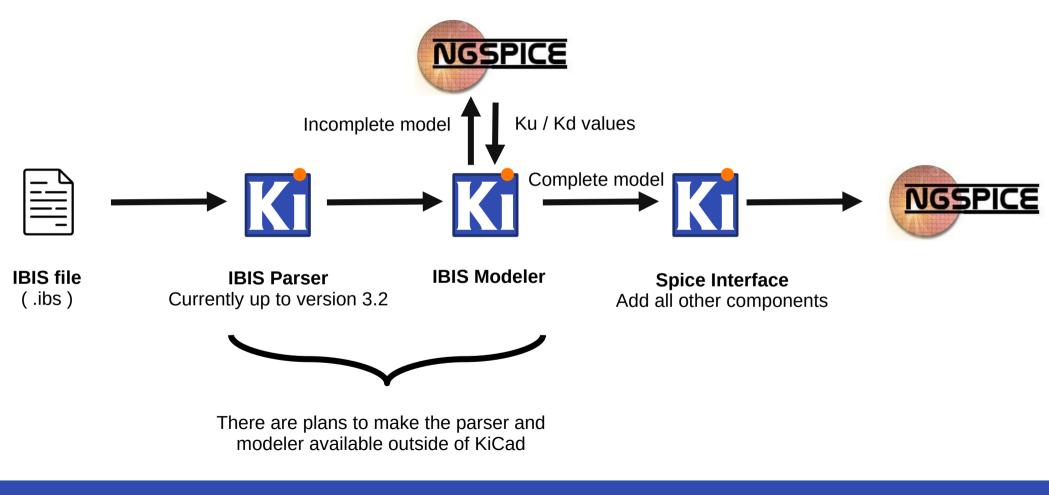

# **IBIS: I/O Buffer Information Specification**

- IBIS ( IO Buffer Information Specification ) is a open file format ( ibis.org )

- It is not a model, but an electrical description of a component

- Manufacturers are reluctant to provide SPICE models

- We can infer a working SPICE model from it

- There is a lot of information that can be extracted:

- Push / pull transistor characteristics

- Imbalance in transistors / differential pairs

- Die capacitance

- Pin capacitance, inductance and resistance

- Much more

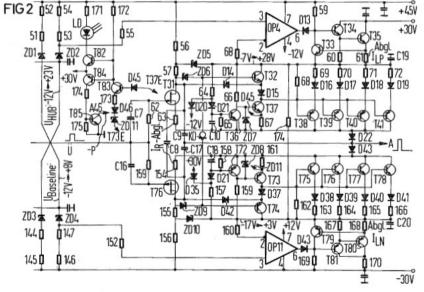

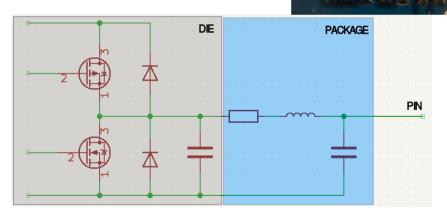

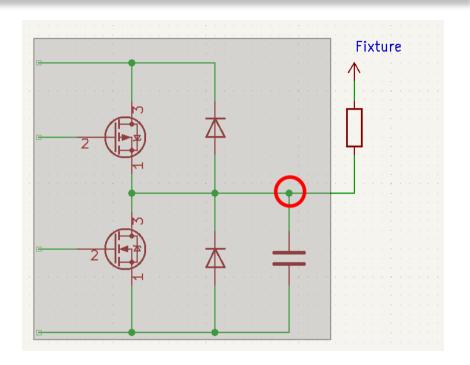

An output / input stage can be complex with a lot of components A model derived from an IBIS description is a lot faster than a full SPICE model

A push-pull output, patent US4329728A, expired

Model that can be used for all IBIS descriptions

#### Package parasitic values

( can be defined for individual pins )

| [Package]                       | 20 TSSO                       | P - PW package                 |                                |

|---------------------------------|-------------------------------|--------------------------------|--------------------------------|

| <br>R_pkg<br>L_pkg<br>C_pkg<br> | typ<br>0.05<br>1.0nH<br>0.2pF | min<br>0.04<br>0.8nH<br>0.16pF | max<br>0.06<br>1.2nH<br>0.24pF |

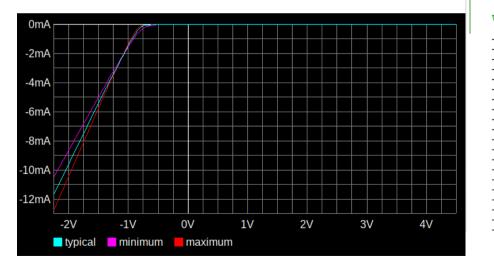

#### Diodes: Current VS voltage tables (IV tables)

#### [GND Clamp] I(typ) I(min) Voltage I(max) -2.25 -0.0127448-0.0117097-0.0104769-1.41975 -0.0047652 -0.00441769-0.00501465-0.00470981 -1.413-0.0043696-0.00495297 -1.36575 -0.00432299 -0.00452237 -0.00403394-1.359 -0.00426788 -0.00446105-0.00398614-1.3455 -0.00415777 -0.00389066 -0.00433856 -1.33875 -0.00410277-0.00384298-0.00427739-1.1565 -0.00263819 -0.00257621 -0.00265617-1.116-0.00232029 -0.00230204 -0.00230743 -1.10925 -0.00226769 -0.0022567 -0.00224985 -0.9675-0.00120242-0.00133869-0.00108784-0.96075 -0.00115444-0.0012972-0.00103574-0.954 -0.94725 -0.00110684-0.001256-0.000984111-0.00105963 -0.00121509-0.000932982 -0.9405-0.00101284-0.00117448-0.000882401-0.93375 -0.000966507 -0.00113421-0.000832418-0.927 -0.000920657 -0.00109428-0.000783091 -0.8595 -0.000498419-0.000718766 -0.000345923-0.85275 -0.000461118-0.000684198-0.000310834-0 846 -0 000425021 -0.000650307-0 000278063

## 26

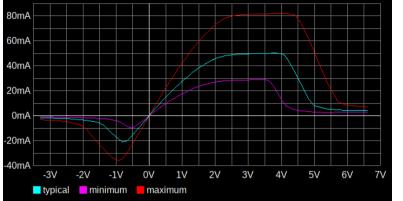

#### Transistor: Current VS voltage tables ( IV tables )

| Voltage I(typ) I(min) I(ma                            | x)                                                                                                         |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 612904<br>829743<br>07052<br>58986<br>61797<br>03398<br>19614<br>93573<br>95344<br>97034<br>06617<br>88613 |

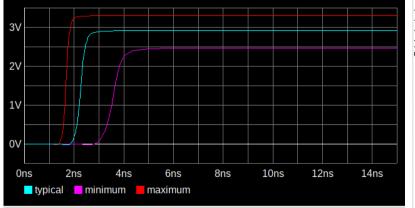

#### Waveforms (VT tables)

| [Rising Waveform]  |

|--------------------|

| V_fixture = 0V     |

| V_fixture_min = OV |

| V_fixture_max = OV |

| R_fixture = 3000hm |

| C_fixture = OF     |

. .

| Time                                                                                                                                                                  | V(typ)                                                                                                                                                                                                         | V(min)                                                                                                                                                                                                              | V(max)                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>1.04121e-09<br>1.30809e-09<br>1.31583e-09<br>1.34039e-09<br>1.3773e-09<br>1.43632e-09<br>1.44917e-09<br>1.46359e-09<br>1.50117e-09<br>1.53949e-09<br>1.55188e-09 | $\begin{array}{c} 6.73865 = -06\\ 0.000830126\\ 0.00104118\\ 0.0010473\\ 0.00106672\\ -0.000967699\\ -0.00415911\\ -0.00485906\\ -0.00564476\\ -0.00564476\\ -0.0076919\\ -0.00977912\\ -0.010454 \end{array}$ | $\begin{array}{c} 1.02646 = -05\\ 0.00052498\\ 0.000656913\\ 0.000660741\\ 0.000691341\\ 0.000720303\\ 0.000726555\\ 0.000726655\\ 0.000733785\\ 0.000752363\\ 0.000771305\\ 0.000771305\\ 0.000777429 \end{array}$ | $\begin{array}{c} 3.59424 \\ \hline 0.00119797 \\ \hline -0.0183515 \\ \hline -0.0176304 \\ \hline -0.00852587 \\ 0.00532204 \\ 0.070565 \\ 0.0918659 \\ 0.119353 \\ 0.212438 \\ 0.350849 \\ 0.408408 \end{array}$ |

| 4 5/0 00                                                                                                                                                              | 0 0110055                                                                                                                                                                                                      | 0 000703434                                                                                                                                                                                                         | 0 4/1/00                                                                                                                                                                                                           |

## **IBIS: How to build a model**

We don't have transient information for the transistors

Falling / rising waveforms are given for a specific load with a fixture voltage ( usually VCC or GND )

We apply time dependent Ku/Kd modifiers to the transistor IV tables. ( 1: current flowing, 0: no current flow ) => Two unknowns

At the point in red, the sum of currents is equal to zero. => One equation

We can have two rising /falling waveforms with two different fixtures.

=> One equation

With 2 unknown and 2 equations, we can easily solve for Ku / Kd With 2 unknown and 1 equations, we have to assume simultaneous switching ( Kd = 1 - Ku )

## We need to build a spice model for each bitstream we want to use

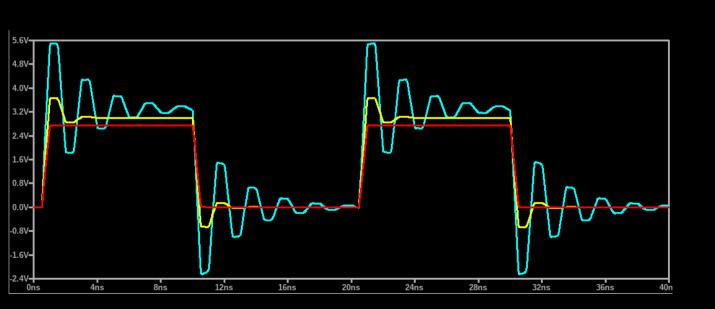

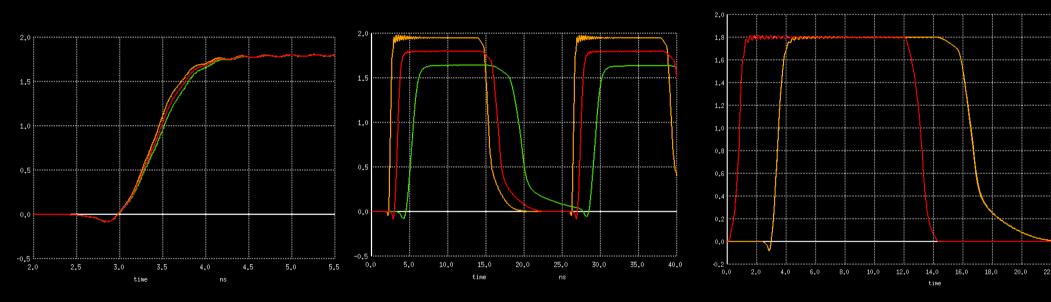

## **IBIS: Simulation examples (SN74HCS244)**

#### Package parasitics Can vary from a chip to another

Supply voltage Typical, minimum and maximum behaviors are defined Modeling accuracy (Red: 0 waveform pairs) (Yellow: 2 waveform pairs)

# Conclusion

- New ways to model things

- IBIS support

- New transmission lines topologies in PCB calculator (eg: differential stripline)

- New simulations accounting for the actual layout:

- Via stress analysis

- Power integrity analysis

- Signal integrity analysis

- Crosstalk analysis

- New features:

- Auto-track width to maintain a constant characteristic impedance

- New DRC rules based on PI / SI

- Add measurements of track delay, capacitance, resistance, etc..

But it's a long road...

### Conclusion

Conclusion:

- KiCad would benefit from advanced simulation capabilities

- Power and signal integrity simulations need PCB simulations

- FEM provides a way to extract information to get a SPICE model

- IBIS provides a way to get accurate and fast SPICE models

Special thanks to:

- Thomas Pointhuber (KiCad)

- Alexandre Halbach (Sparselizard)

- Holger Vogt (ngspice)

- The KiCad team

potential 0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

# Thank you for attention