#### Links

- https://gitlab.com/bwidawsk/gemu

- cxl-2.0v<latest> branch

- https://gitlab.com/bwidawsk/linux

- cxl-2.0v<latest> branch

- https://github.com/pmem/ndctl

- cxl-2.0v<latest> branch

- https://www.computeexpresslink.org/download-the-specification

SSE SYSTEM SOFTWARE ENGINEERING

intel

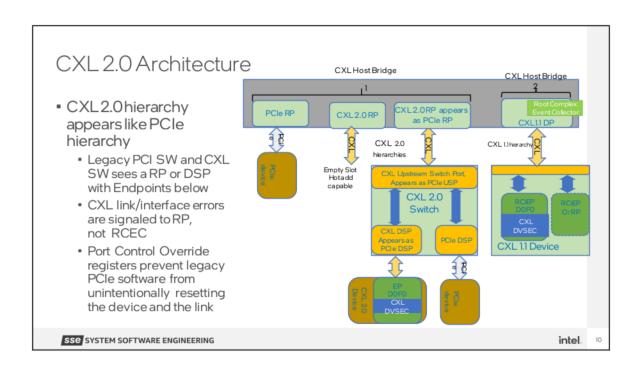

- CXL 2.0 has significant changes.

- CXL 1.1 support isn't even there yet, so there really isn't anything to start with.

- Starting before the spec is even complete.

How to get a Linux device driver upstream, by the time internal and external partners receive silicon?

#### End Goal

#### T minus 6 months

- Linux CXL 2.0 memory device drivers within 0 days of spec release

- Validate the spec

- Enable hardware vendors and validation

- Have some reusable infrafor regression testing

- Potential use for guests

- Masters of our own destiny.

SSE SYSTEM SOFTWARE ENGINEERING

intal

- In 6 months, have a well tested Linux driver sent on the day the spec is released.

- Whatever environment is used should have some future use.

- Don't be encumbered by the plans/schedules of others.

#### Pre-silicon state of the art

- Hardware

- No 2.0 FPGAs available

- No 1.1 hardware available

- Prior art

- NVDIMM faked it all in Linux

- QEMU CCIX patches

SSE SYSTEM SOFTWARE ENGINEERING

intel

There was no prior art of much value.

CXL 2.0

SSE SYSTEM SOFTWARE ENGINEERING intel. 7

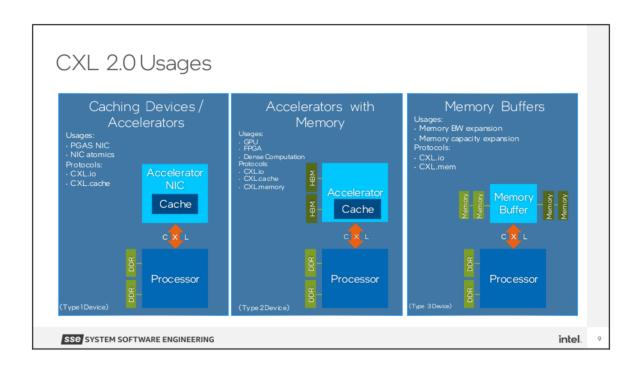

## CXL 2.0 High Level

- Open industry standard for high bandwidth, low-latency interconnect

- Connectivity between host processor and accelerators/ memory device/ smart NIC

- Addresses high-performance computational workloads across AI, ML, HPC, and Comms segments

- Heterogeneous processing: scalar, vector, matrix, spatial architectures spanning CPU, GPU, FPGA

- Memory device connectivity

- PCIe PHY completely leveraged with additional latency optimization

- Dynamic multiplexing of 3 protocols

- Based on PCle® 5.0 PHY infrastructure

- Leverages channel, retimers, PHY, Logical, Protocols

- CXL.io I/O semantics, like PCIe mandatory

- CXL.cache Caching Semantics optional

- CXL.mem Memory semantics optional

SSE SYSTEM SOFTWARE ENGINEERING

intel.

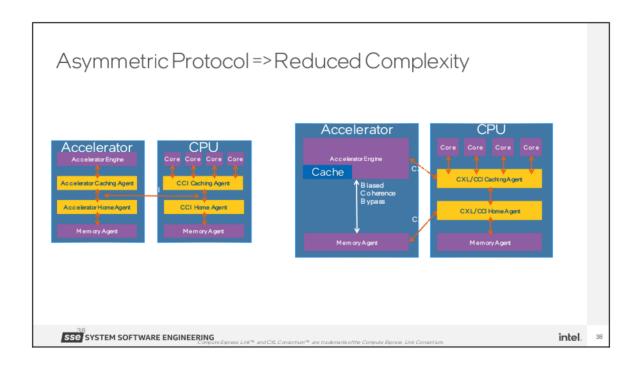

QEMU is a good for CXL enabling because it's open source and very featureful. CXL is an industry wide standard. A lot of different parties want lots of different things with different priorities.

Making a useful platform for everyone will increase adoption and make it more useful to everyone.

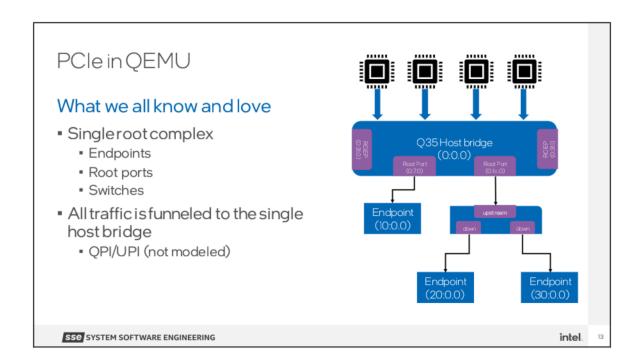

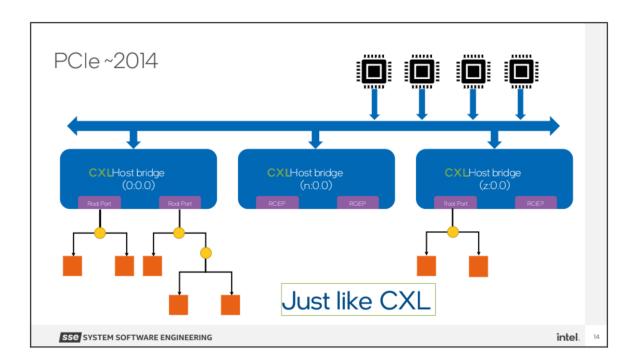

This is what a modern platform actually looks like.

CXL is building on top of a modern platform.

Is this going to work with Q35?

## Options

- Use a single host bridge

- Fine for basic driver bring-up

- Limited for interleave scenarios

- Risk?

- Replace Q35 with something new

- A lot of work for not much gain (for CXL)

- Support Burden

- PXB

- Good compromise

SSE SYSTEM SOFTWARE ENGINEERING

intal

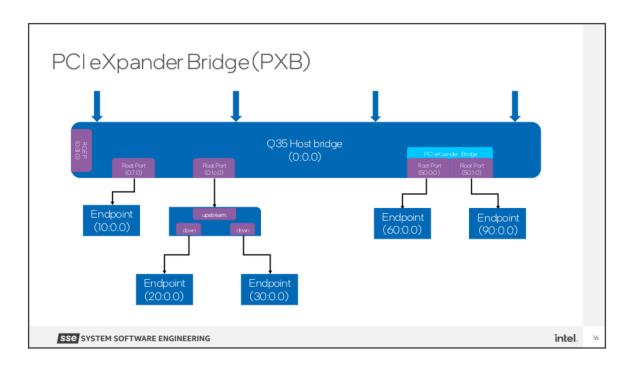

Single host bridge limits testable use-cases and risks adding bugs to core functionality. We need something that understands multiple host bridges, and a new thing would work.

PXB solves the issue in a perfectly acceptible way.

A PXB kind of looks like a PCI-PCI bridge architecturally. This allows us to keep existing PCIe mechanisms while introducing distinct CXL topologies (including interleave across PXBs)

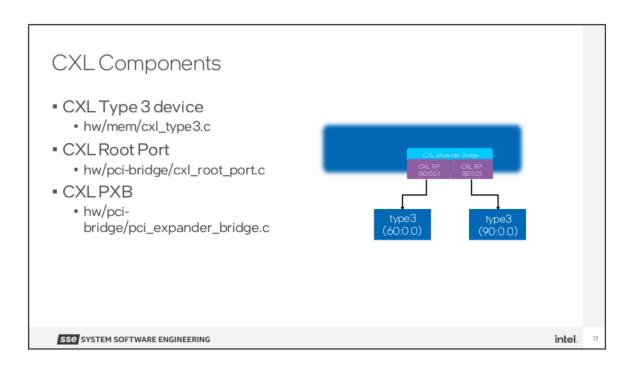

Now we can get to emulating the different components...

#### **CXL** utilities

## hw/cxl/\*

- cxl-component-utils.c

- DVSEC helpers

- .cache/mem MMIO handler

- cxl-device-utils.c

- Device MMIO

- Memory device MMIO

- Mailbox MMIO

- cxl-mailbox-utils.c

- Mailbox command implementations

- pci\_expander\_bridge.c

- New CXL PXBisms

- MMIO for host bridge

- Windows (\*not spec'd)

- cxl\_root\_port.c

- PCle root port setup

- DVSEC initialization

SSE SYSTEM SOFTWARE ENGINEERING

intel.

So many components and utility libraries just for a simple "Hello World"

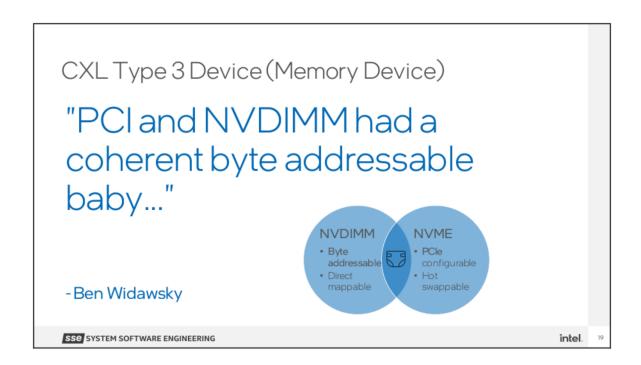

The code very clearly indicates it's PCI + a memory device. Specifically (not exclusive to a type 3 device), mailbox handling sets it apart.

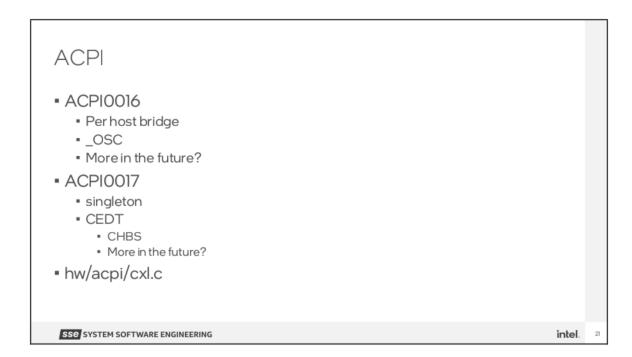

CXL requires ACPI per the spec to be useful. QEMU provides everything we need to make it work.

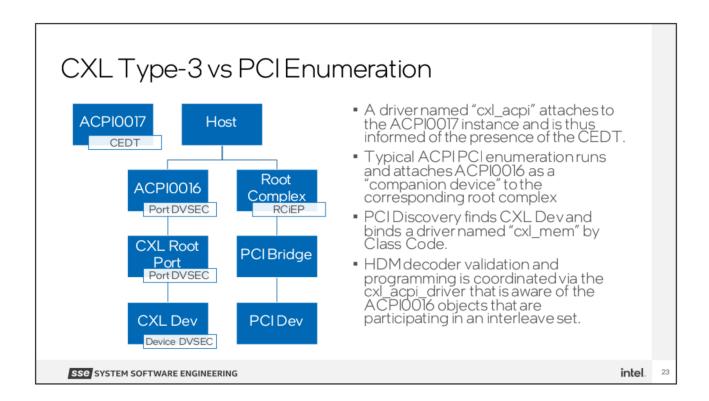

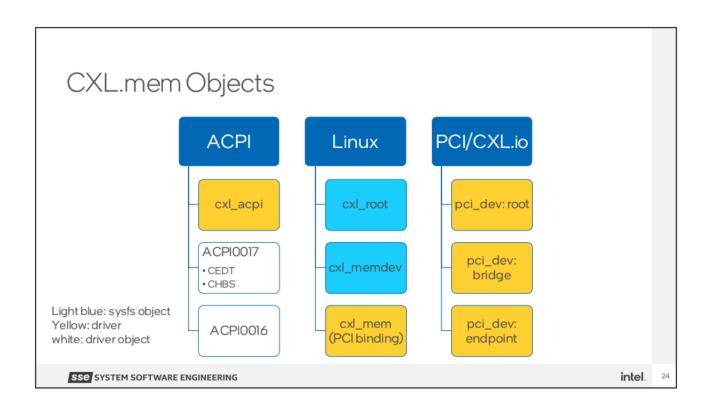

CXL and PCI enumeration are distinct. CXL can be thought of as an overlay to PCIe that is accomplished via DVSEC and MMIO.

# Interfacing with $\mathsf{CXL}$

- Sysfs

- /sys/bus/cxl/

- IOCTL

- QUERY

- SEND

- Managed command set

- RAW escape command

- Future

- Error reporting

SSE SYSTEM SOFTWARE ENGINEERING

intel

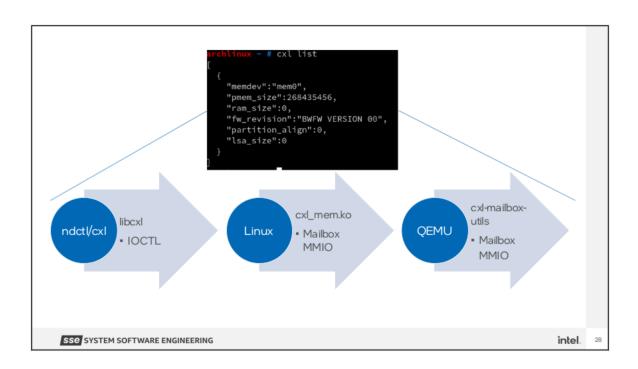

# Putting it all together

- QEMU Emulation

- Memory region

- MMIO

- Mailboxes

- Kernel driver

- Documentation!

- Tools

- 2.0 spec is available

SSE SYSTEM SOFTWARE ENGINEERING

hal.

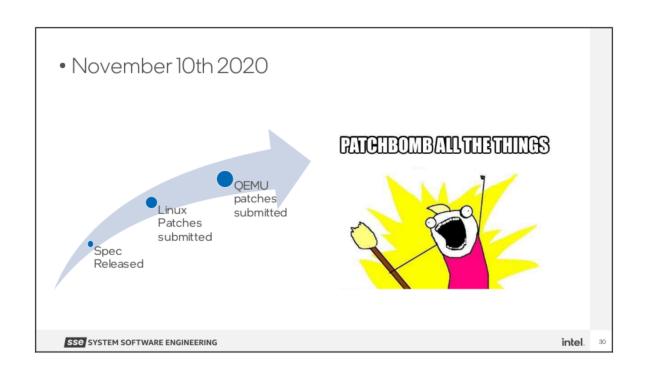

## Results

- QEMU v2 patches sent

- Minimal review

- Linux driver v3 sent

- Moderate review

- Nothing upstream

- Still no hardware to test on

- Still no other viable pre-silicon platform to test on.

- Made our deadline!

- This talk!!!

SSE SYSTEM SOFTWARE ENGINEERING

intel

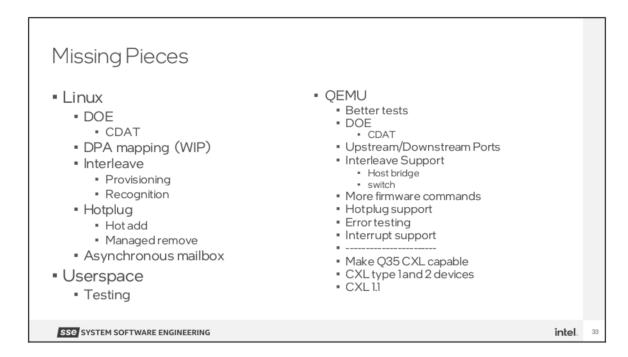

Everything below dashed line is not of importance to my team. Interleave and CDAT are probably the next things we really need.

# Making it useful

- qemu-system-x86\_64

- -machine q35,<cxl>

- -object memory-backend-file,id=cxl-mem1,share,mem-path=cxltype3,size=512M

- -device pxb-cxl,id=cxl.0,bus=pcie.0,bus\_nr=52,uid=0,len-window-base=1,window-base[0]=0x4c0000000,memdev[0]=cxl-meml

- -device cxl-rp,id=rp0,bus=cxl.0,addr=0.0,chassis=0,slot=0

- -device cxl-type3,bus=rp0,memdev=cxl-mem1,id=cxl-pmem0,size=256M

- CXL utilities part of ndctl being developed

- https://github.com/pmem/ndctl/tree/cxl-2.0vl

SSE SYSTEM SOFTWARE ENGINEERING

intel

## Thanks

- $\blacksquare \ \mathsf{Mahesh} \, \mathsf{Natu-CXL} \, \mathsf{architectural} \, \mathsf{diagrams} \, \mathsf{and} \, \mathsf{high} \, \mathsf{level}$

- Dr. Debendra Das Sharma CXL usages

- Dan Williams Linux diagrams

SSE SYSTEM SOFTWARE ENGINEERING

intel.

Well, thanks for your ears and eyes. I hope you got something out of it, and I look forward to any feedback people might have.

# CXL1.1-> CXL2.0

| Feature                              | Description                                                                                                                                                                                                                                                                                           |     |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| CXL PCle End-Point                   | CXL device to be discovered as PCle Endpoint Support of CXL11 devices directly connected to Root-Port or Downstream Switch Port                                                                                                                                                                       |     |

| Switching                            | Single level of switching with multiple Virtual Hierarchies (cascaded possible in a single hierarchy) CXL Memory Fan-Out & Pooling with Interleaving CXL.Cache is direct routed between CPU and device with a single caching device within a hierarchy. Downstream portmust be capable of being PCIe. |     |

| Resource Pooling                     | Memory Pooling for Type3 device – Multiple Logical Device (MLD), a single device to be pooled across 16 Virtu<br>Hierarchies.                                                                                                                                                                         | ual |

| CXL.cache<br>CXL.mem<br>enhancements | Persistence (Global Persistence Flush), Managed Hot-Plug, Function Level Reset Scope Clarification, Enhanced Flor CXL Cache/Mem, Memory Error Reporting and QoS Telemetry                                                                                                                             | LR  |

| Security                             | Authentication and Encryption - CXL.IO uses PCIe IDE, CXL defines similar capability for CXL.Mem                                                                                                                                                                                                      |     |

| Software<br>Infrastructure/ API      | ACPI & UEFI ECNs to cover notification and management of CXL Ports and devices CXL Switch API for a multi-host or memory pooled CXL switch configuration and management                                                                                                                               |     |

|                                      |                                                                                                                                                                                                                                                                                                       |     |

| SSE SYSTEM SOFTWARE ENGINEERING      |                                                                                                                                                                                                                                                                                                       | ir  |