## TUTORIAL MY FIRST FPGA DESIGN

Tristan Gingold - tgingold@free.fr - FOSDEM'18

# IT'S A TALK ABOUT HARDWARE!

Things like that...

There are many talks at FOSDEM about software. Try a different room

# IT'S A TALK ABOUT CHIP DESIGN

This

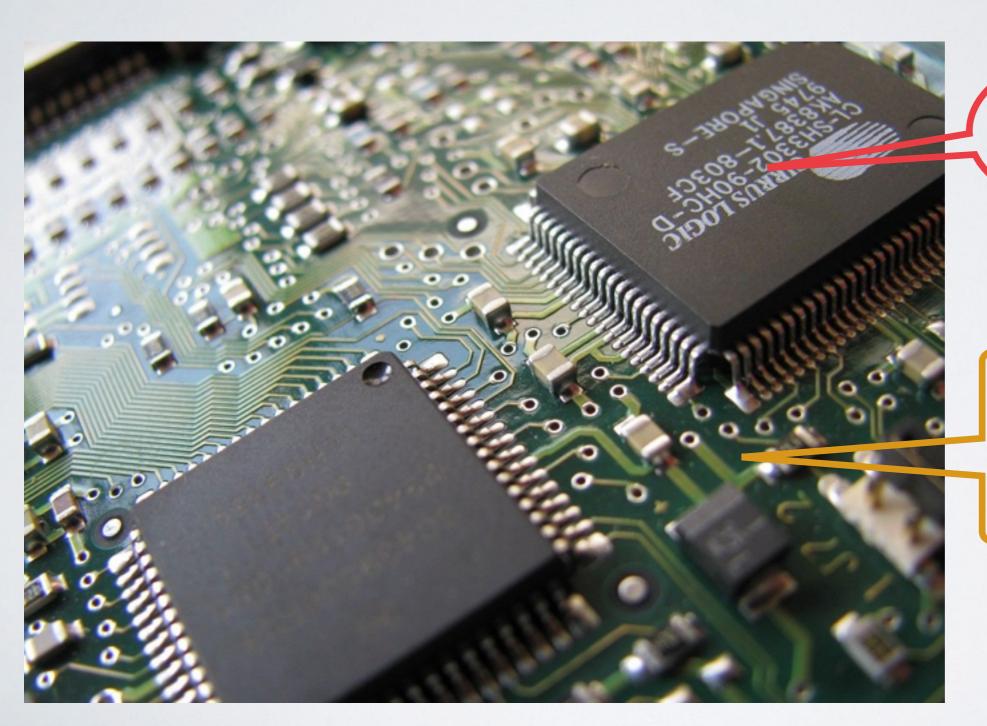

This is a PCB

(Printed Circuit Board)

KiCad is a tool to design

boards, you also need

electronic knowledge

# MORE SPECIFICALLY, DIGITAL CHIPS

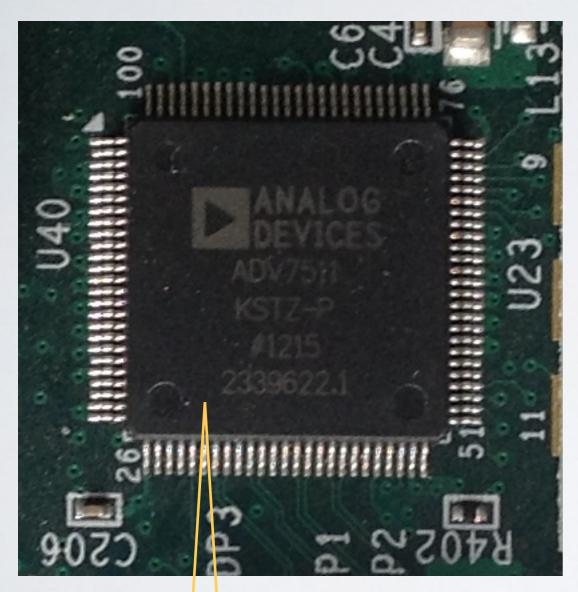

Digital chip

Analog chip

See the difference?

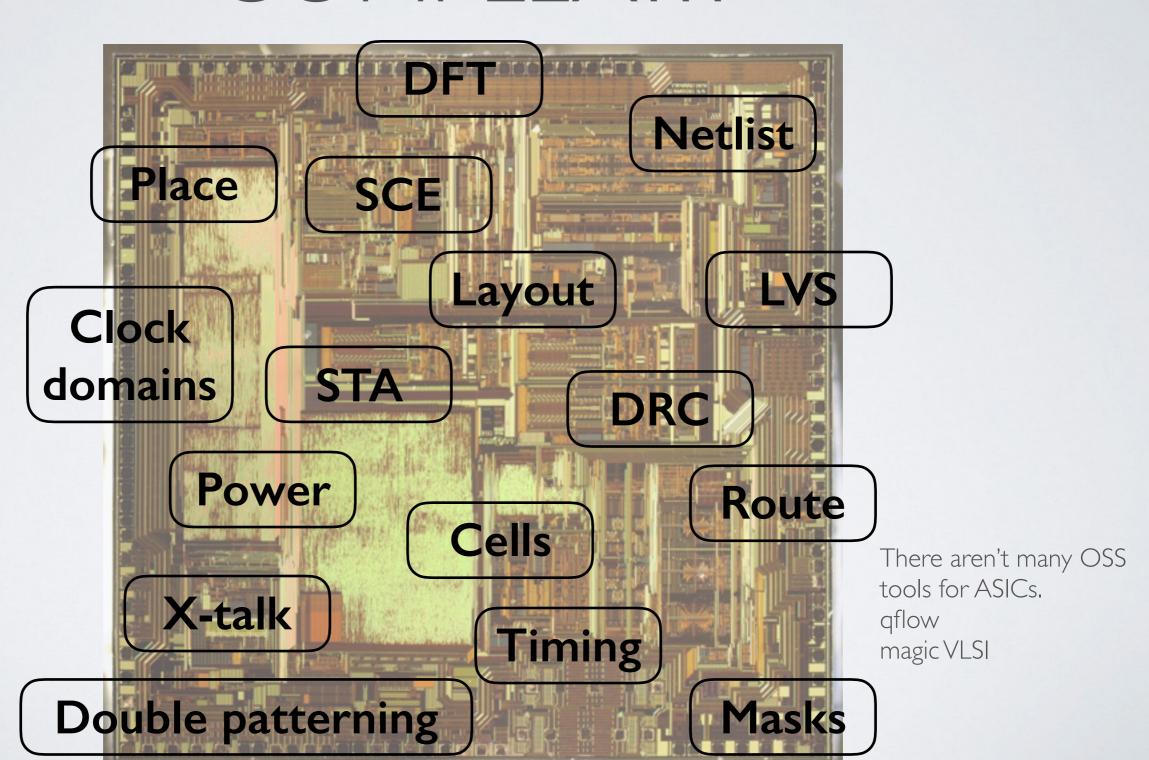

## DESIGNING AN IC IS COMPLEX...

### ... AND VERY EXPENSIVE

ASML lithography machine Expect \$\$\$ for the first chip...

# BUT SOME ARE PROGRAMMABLE!

Normal chip

FPGA

There are other kinds of programmable circuits:

Gate array

CPLD

. .

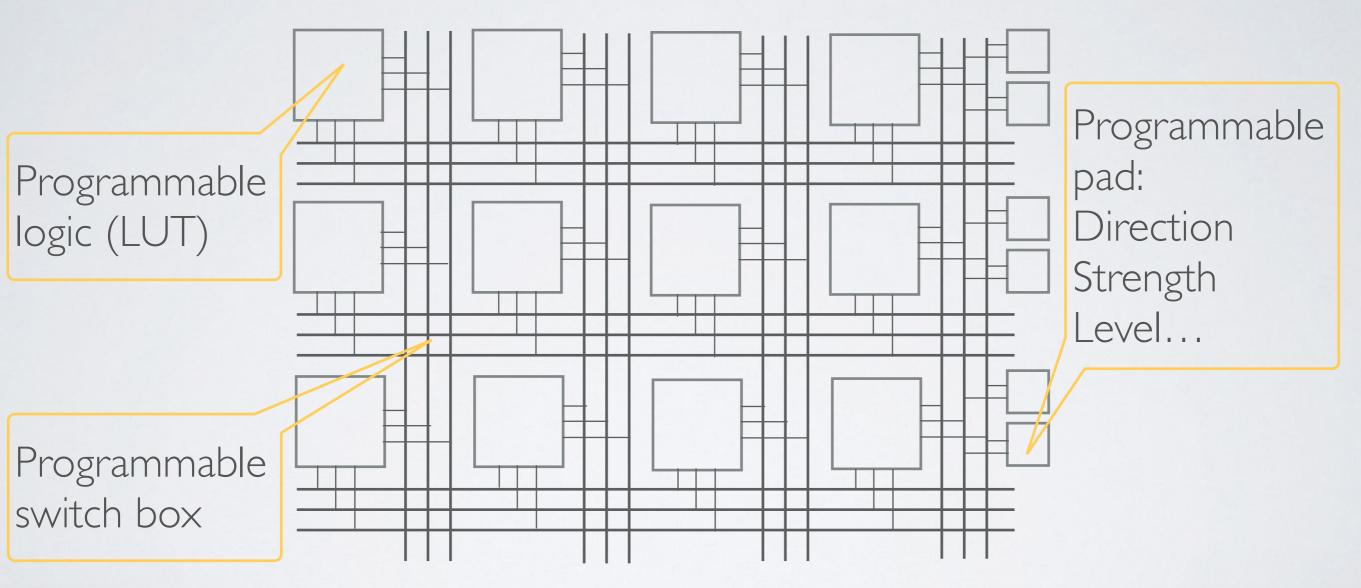

### FPGA ARCHITECTURE

That's a very simple view...

Most FPGAs also have PLL, memories, multipliers, or even SERDES/PCI-e blocks. See FPGA databooks

#### DIGITAL IS ABOUT 0 AND I

That's simple!

Assuming you know about binary computation

For analog design, see gnucap, qucs, spice...

(There are always analog parts in a circuit)

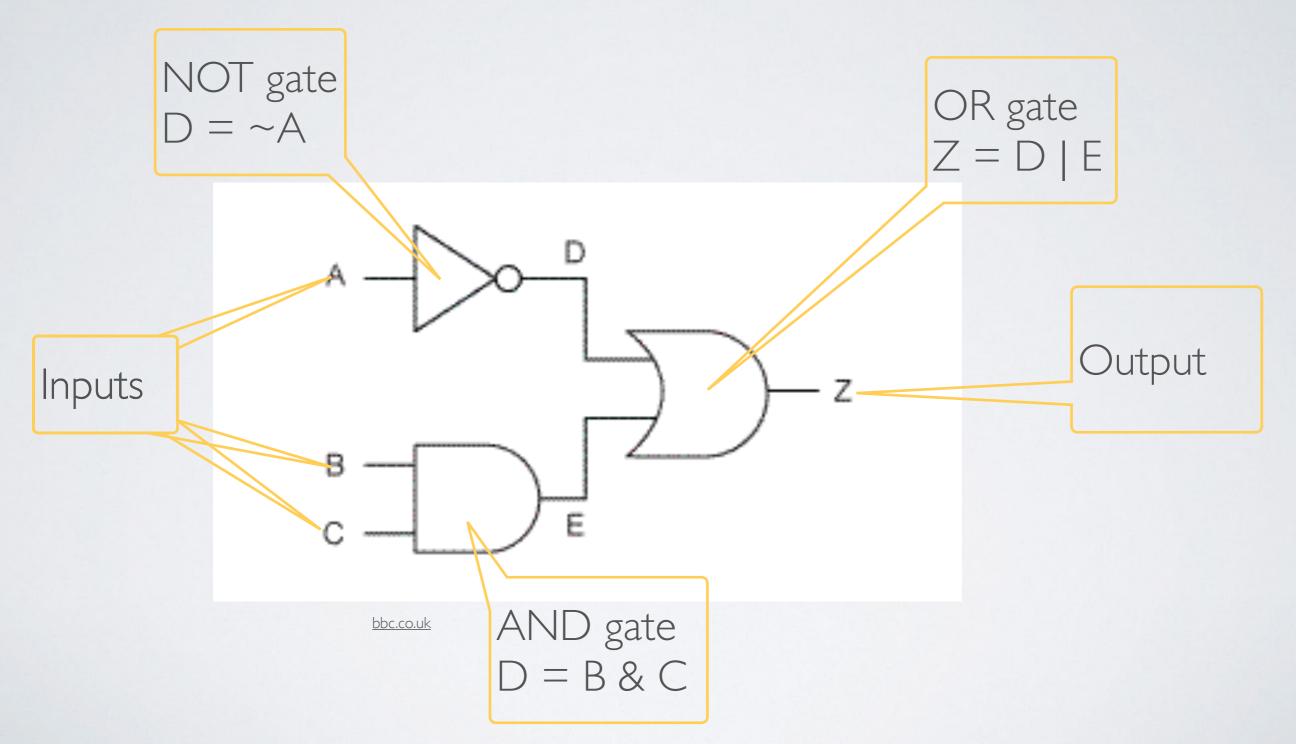

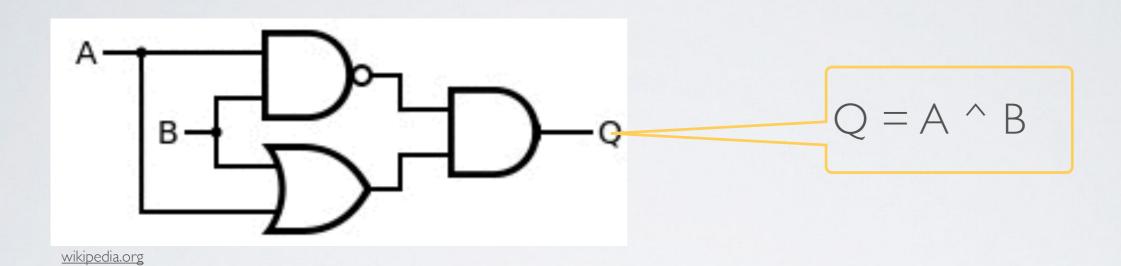

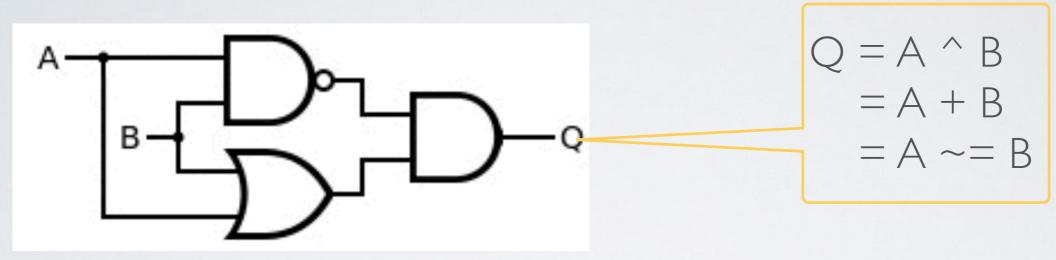

## DIGITAL IS ABOUT LOGIC BASIC OPERATIONS

### COMBINE THEM!

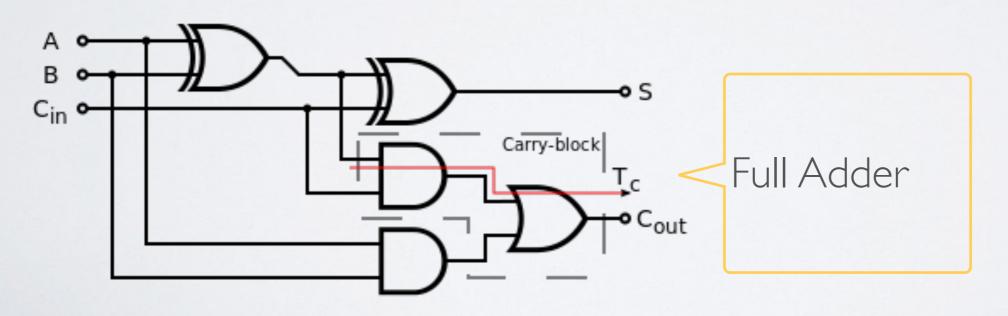

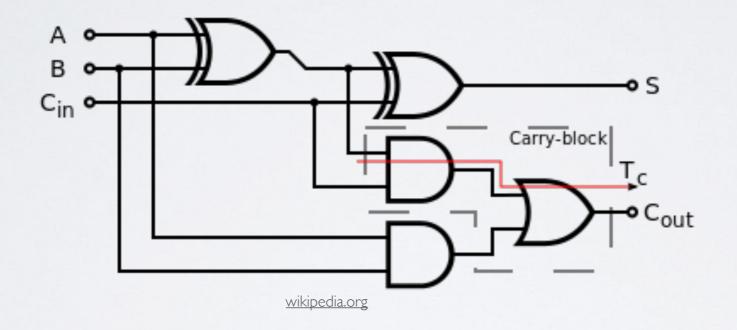

### OR DO MATH (ONE BIT)

wikipedia.org

| А | В | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 |   |   |

| 1 | 0 | I |

|   |   | 0 |

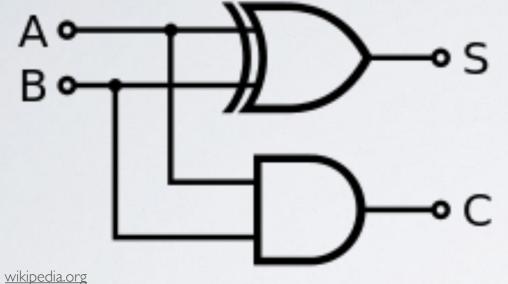

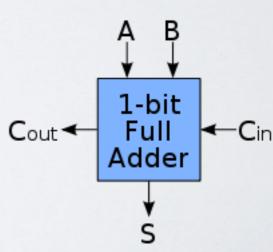

#### THEADDER

S:SUM C: CARRY

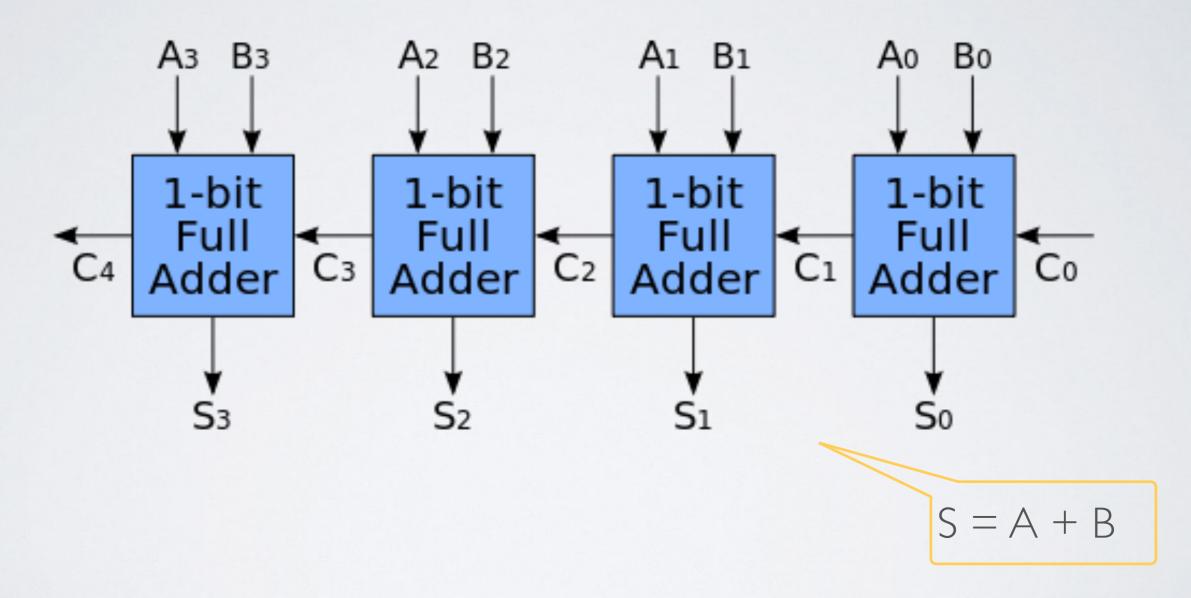

#### MULTIPLE BIT ADDER

There are more efficient way to design large adders Search for Digital Logic Architecture

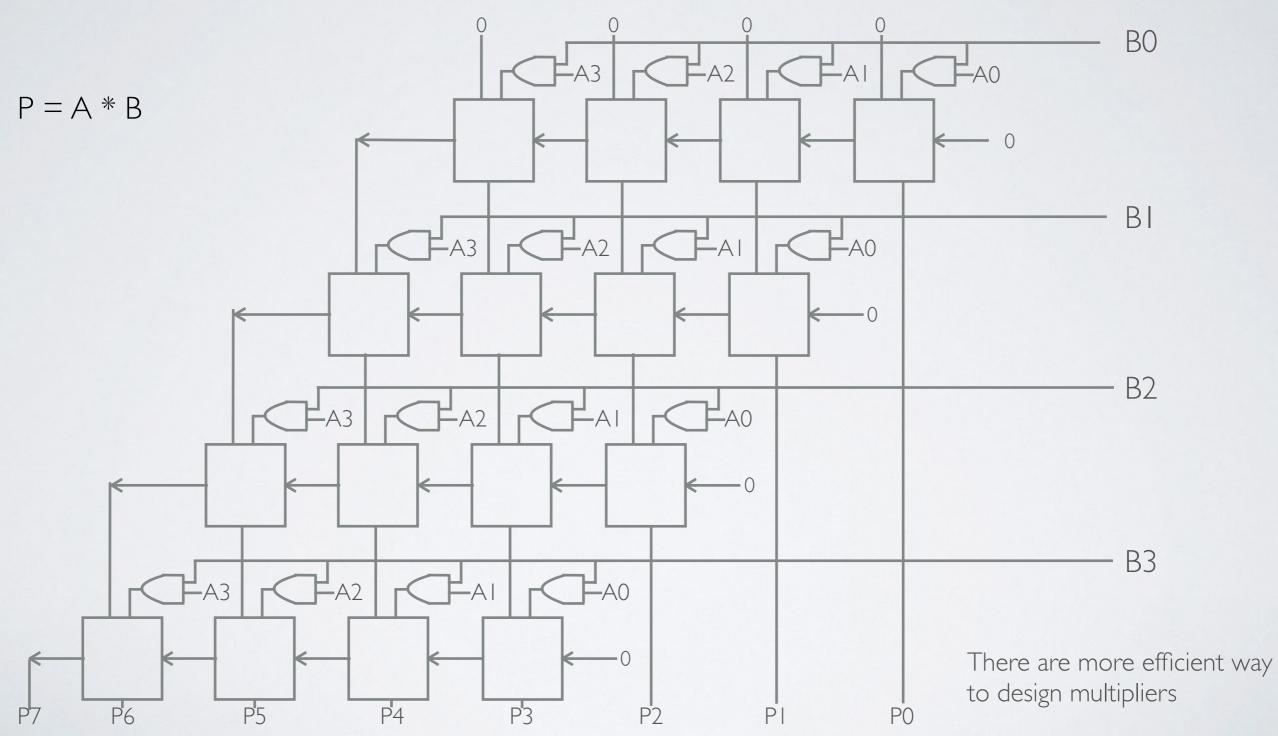

## IFYOU CAN ADD, YOU CAN MULTIPLY!

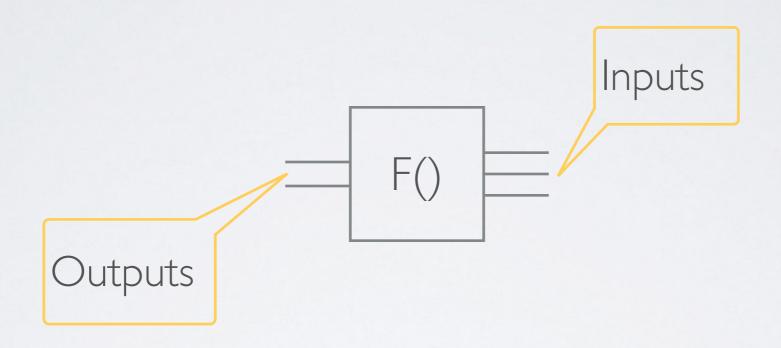

### YOU CAN DESIGN ANY LOGICAL/ARITH FUNCTION

Well, many functions...

But this is not very efficient (can take a lot of gates)

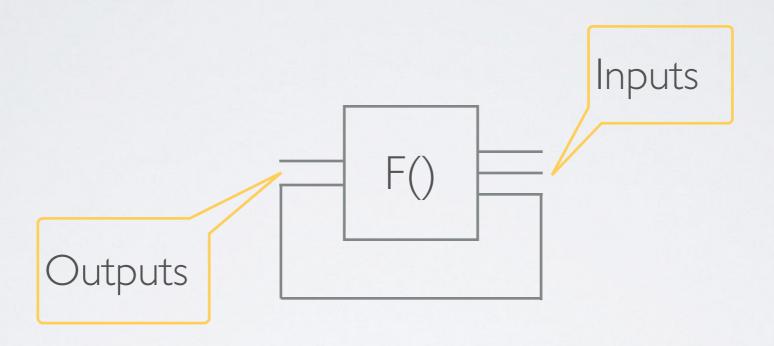

# MORE POWERFUL: RECURSION!

In math, recursion is very powerful.

In digital design, it doesn't work directly!

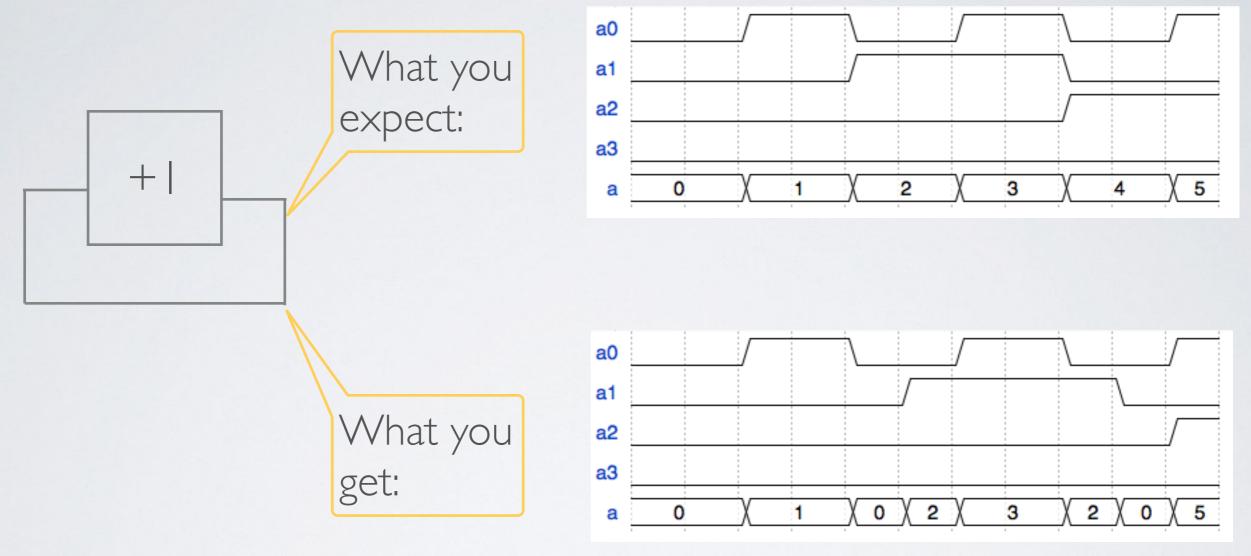

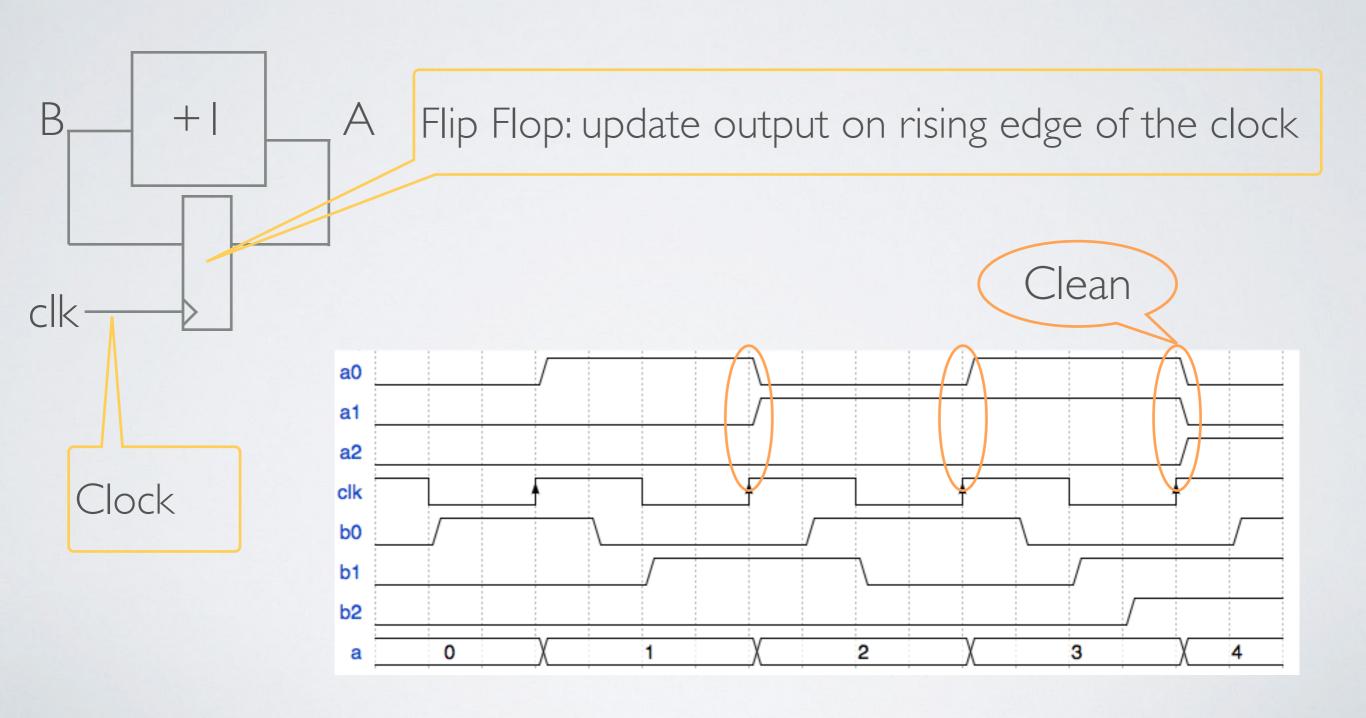

### TIMING SYNCHRONISATION

Do you remember the full adder?

It takes time for a signal to propagate through gates. (due to capacities).

So the arrival times at S and Cout differ.

#### TIMING DIAGRAM

Thanks to <a href="http://wavedrom.com/editor.html">http://wavedrom.com/editor.html</a>

Outputs are not available at the same time.

#### SYNCHRONOUS DESIGN

You can try to balance paths, but:

- It's very hard

- propagation time depends on too many factors

You can use a logic that is not affected by delay variation (like gray code), but:

works only in some cases.

Rule #1:

no direct loop/feedback

### SYNCHRONOUS DESIGN

#### DIGITAL DESIGN

#### It's a mix of:

- logic gates

- •flip flops

There are other way to synchronise (latch, falling edge, double edge...)

It is possible to use schematic editors, but

- tedious

- doesn't scale well

Use an HDL

Hardware Description Language

I will use VHDL

## MY FIRST DESIGN BLINKING LEDS

latticesemi.com

Leds

#### Using OSS tools:

- ghdl

- yosys

- •arachne-pnr

- •iceStorm

Target: Lattice iCEstick ~ 22 euros

Supported by OSS tools

#### VHDL: EXTERNAL INTERFACE

```

boilerplate

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

Led positions

Comment

D3

(to not forget

D2 D5 D4

leds position)

interface

D1

entity leds is

port (clk : in std_logic;

led1, led2, led3, led4, led5 : out std_logic);

end leds;

Input: clock

outputs: leds

(externally generated 3Mhz)

```

#### Internals

#### INTERNALS

```

Process:

concurrent

execution,

triggered on

clk

```

```

Internal

architecture blink of leds is

wire

signal clk_4hz: std_logic;-

begin

process (clk)

variable counter: unsigned (23 downto 0);

begin

if rising_edge(clk) then

if counter = 2_999_999 then

counter := x''0000000'';

clk_4hz <= not clk_4hz;

else

counter := counter + 1;

end if:

end if;

end process;

led1 <= clk_4hz;</pre>

led2 <= clk_4hz;</pre>

concurrent

led3 <= clk_4hz;</pre>

assignments

led4 <= clk_4hz;</pre>

led5 <= clk_4hz;</pre>

```

There are many VHDL or Verilog tutorials on the web. end blink;

#### SYNTHESIS

Translating (or compiling) sources to gates (netlist)

```

First, analysing sources:

ghdl -a leds.vhdl

ghdl -a blink.vhdl

Synthesis:

yosys -p 'ghdl leds; synth_ice40 -blif leds.blif'

synthesis script

```

frontend command

#### PLACE & ROUTE

Allocate resources on the FPGA

device

input

arachne-pnr -d 1k -o leds.asc -p leds.pcf leds.blif

output

place file

set\_io led1 99

set\_io led2 98

set\_io led3 97

set\_io led4 96

set\_io led5 95

set\_io clk 21

IC pin #

#### PROGRAM

Write into the FPGA

USB interface

flash

Create the binary file:

icepack leds.asc leds.bin

Write to flash:

iceprog leds.bin

The FPGA is automatically reset and then load the new config

#### TOOLS USED

Synthesis: <a href="http://www.clifford.at/yosys/">http://www.clifford.at/yosys/</a>

VHDL front-end: <a href="https://github.com/tgingold/ghdlsynth-beta">https://github.com/tgingold/ghdl</a><a href="https://github.com/tgingold/ghdl">https://github.com/tgingold/ghdl</a>

Place and route: <a href="https://github.com/cseed/arachne-pnr">https://github.com/cseed/arachne-pnr</a>

iCE40 tools: <a href="http://www.clifford.at/icestorm/">http://www.clifford.at/icestorm/</a>

### QUESTIONS?